本节主要介绍了FPGA底层资源,包括IOB、PLL、MMCM、CLB、LUT等

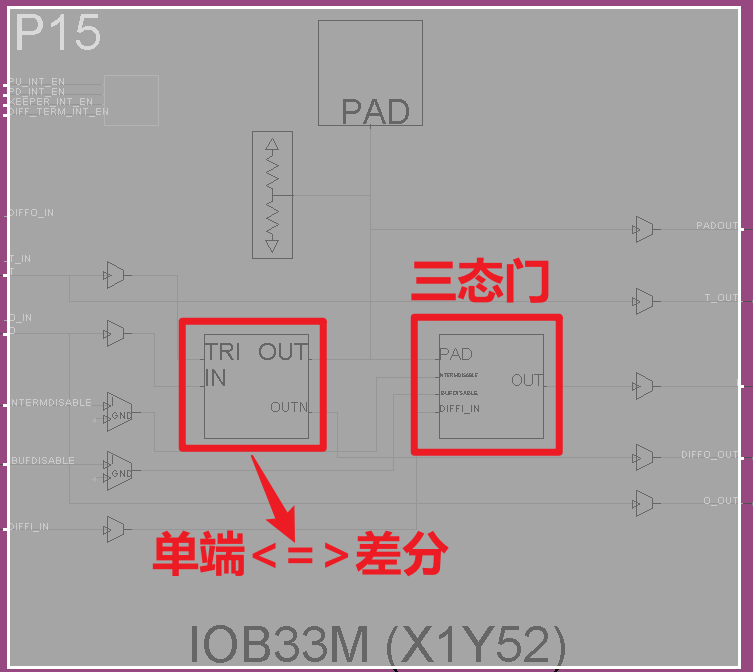

IOB

IO口的管理单元,可编程输入输出单元

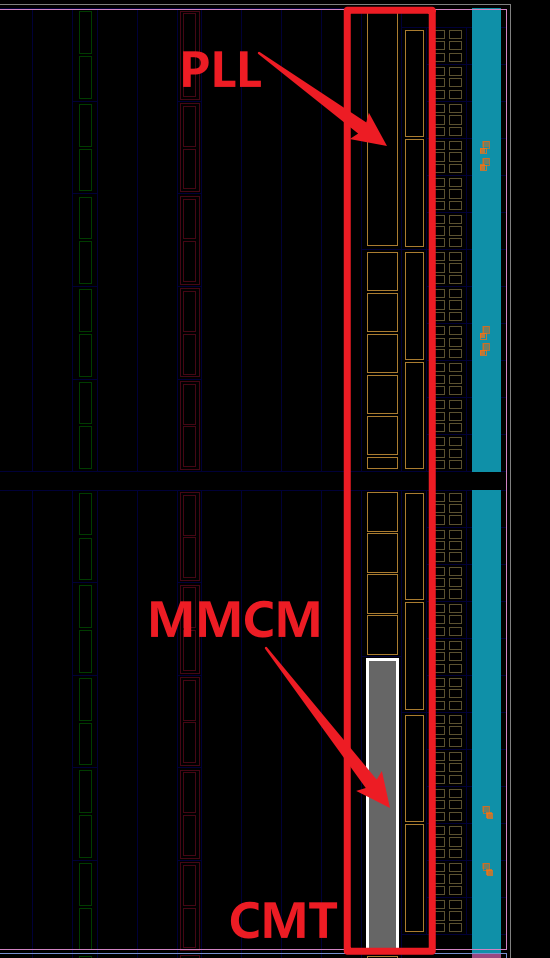

CMT

Clock Manage Tile,时钟管理模块

一个CMT主要由一个MMCM(调频范围比较大,调频也比较准)和一个PLL(调相位比较准)组成

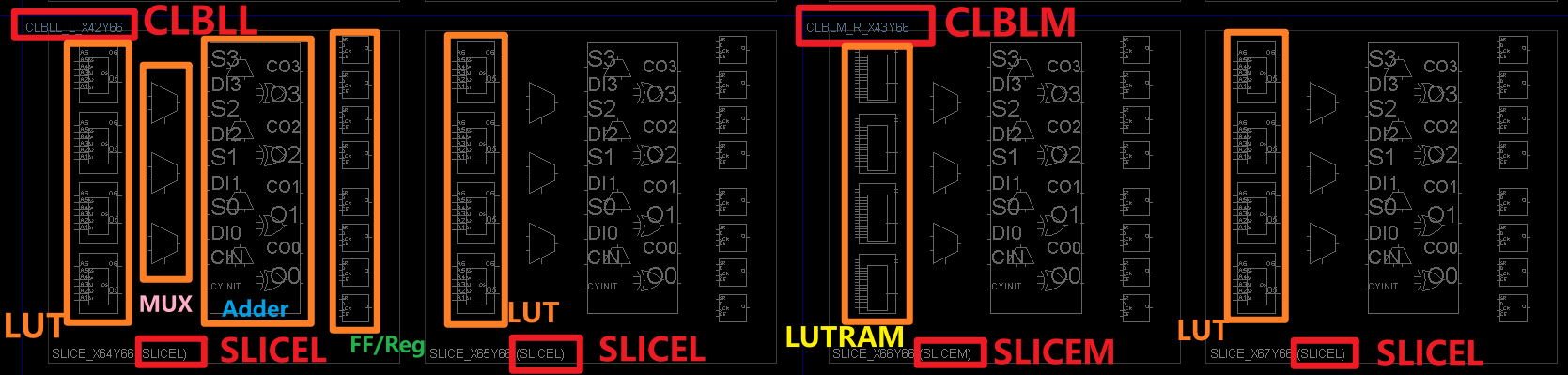

CLB

Configurable Logic Block,可编辑逻辑块

CLB分为CLBLM与CLBLL

- CLBLM:SLICEL+SLICEM

- CLBLL:SLICEL+SLICEL

与7系列(以上)的一个CLB包含两个Slice不同的是Ultrascale中一个CLB只有一个Slice

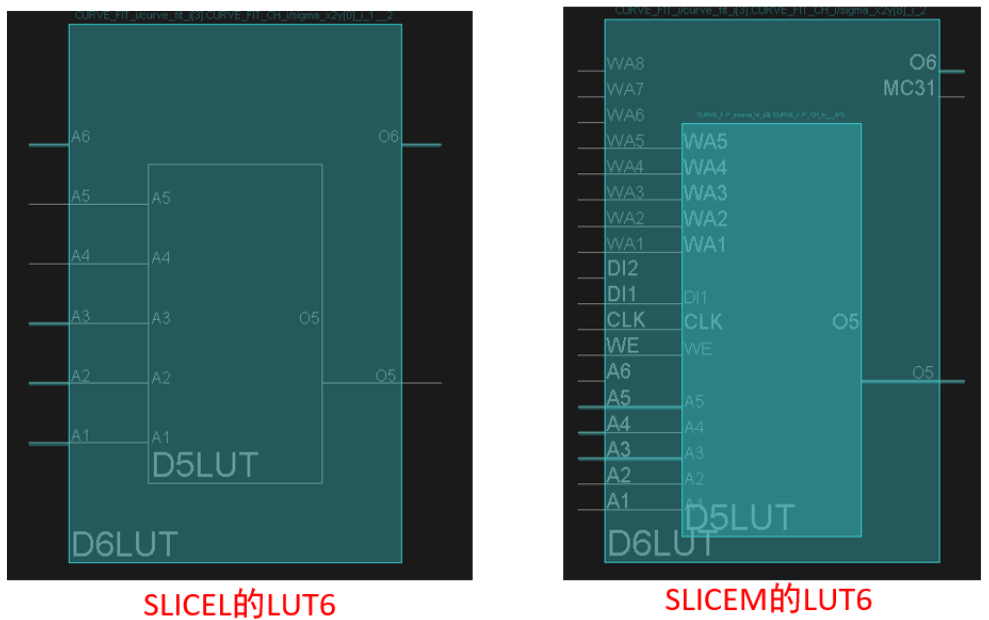

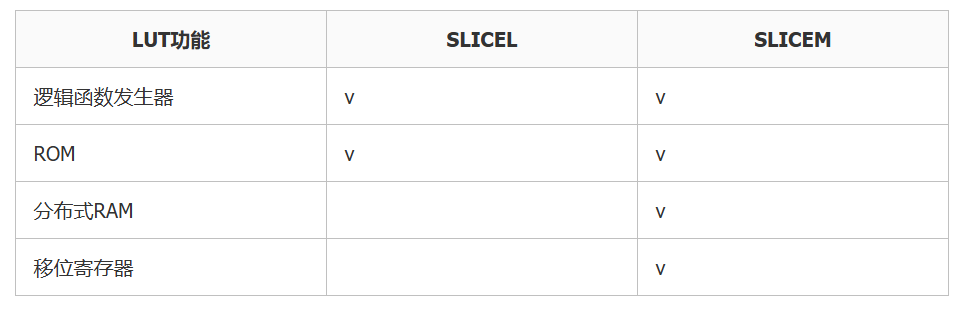

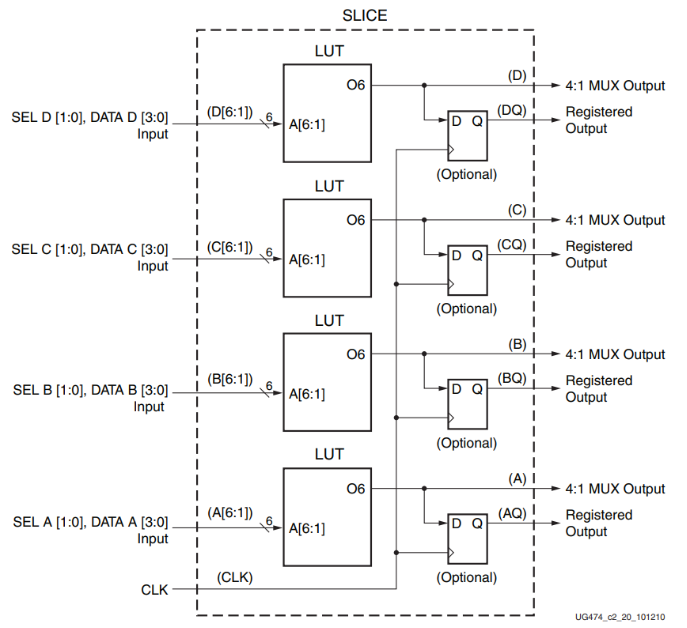

1.LUT6

虽然SLICEL和SLICEM的结构组成一样,但两者更细化的结构上略有不同,区别在于LUT6上(如下图所示),从而导致LUT6的功能有所不同(如下表格所示)。

不论是SLICEL还是SLICEM,他们的LUT6都可以作为ROM使用,配置为64x1(占用1个LUT6,64代表深度,1代表宽度)、128x1(占用2个LUT6)和256(占用4个LUT6)的ROM

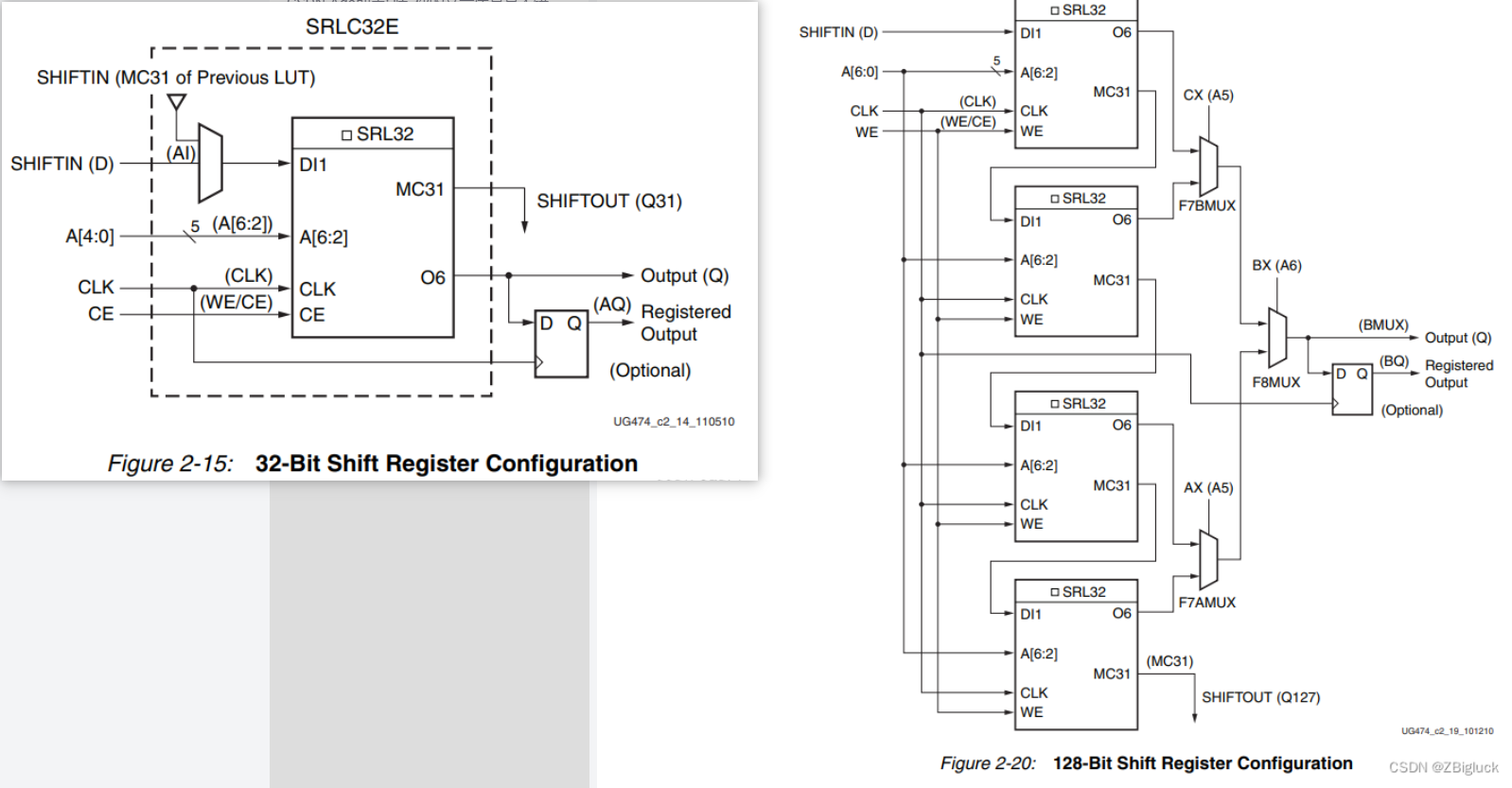

SLICEM中的LUT还可以配置为移位寄存器,每个LUT6可实现深度为32的移位寄存器,且同一个SLICEM中的LUT6(4个)可级联实现128深度的移位寄存器

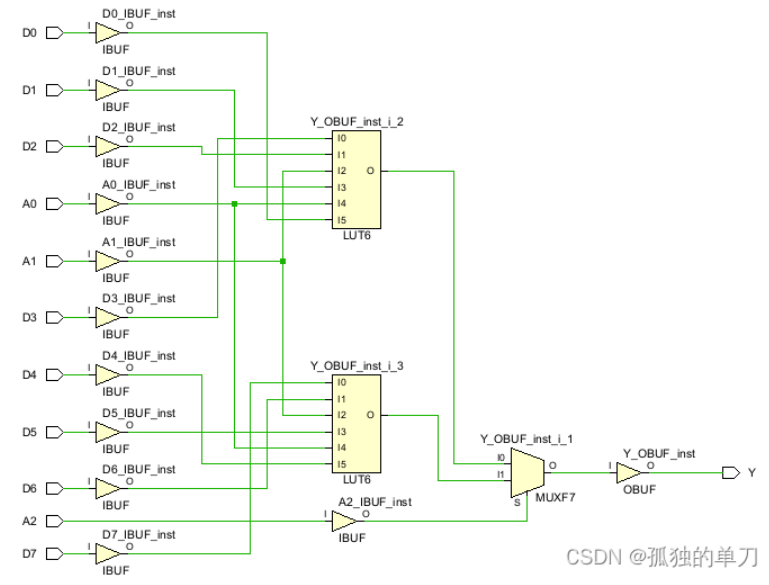

查找表(look-up-table)简称为 LUT, LUT 本质上就是一个 RAM。每一个 LUT 可以看成一个有 6 位地址线的 64x1 的 RAM。 当用户通过原理图或 HDL 语言描述了一个逻辑电路以后, PLD/FPGA 开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入 RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可

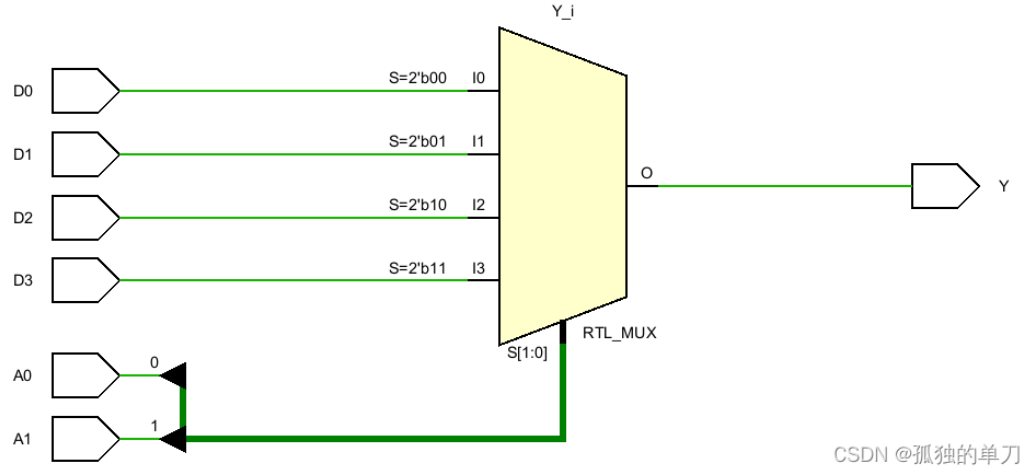

2.MUX

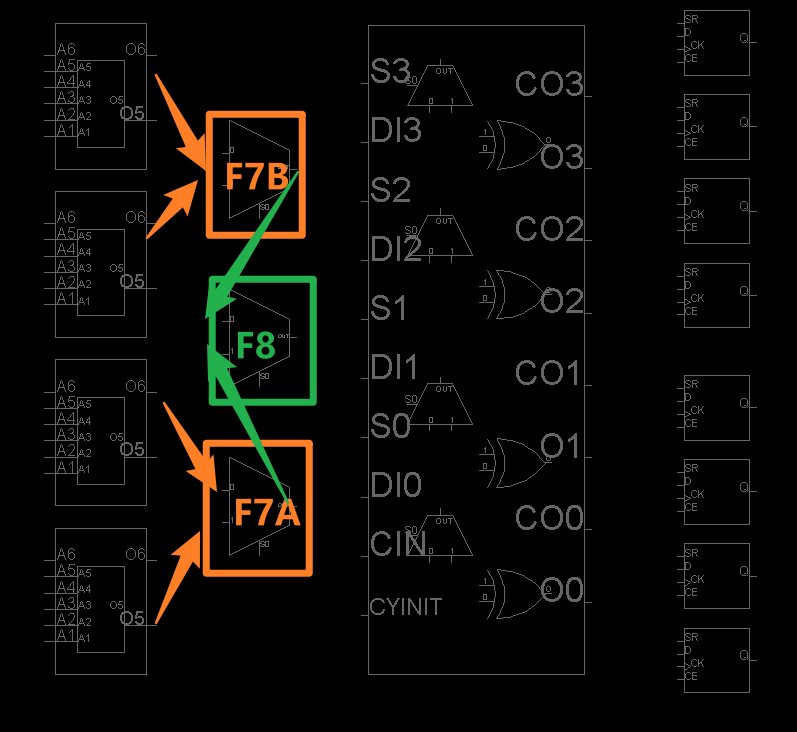

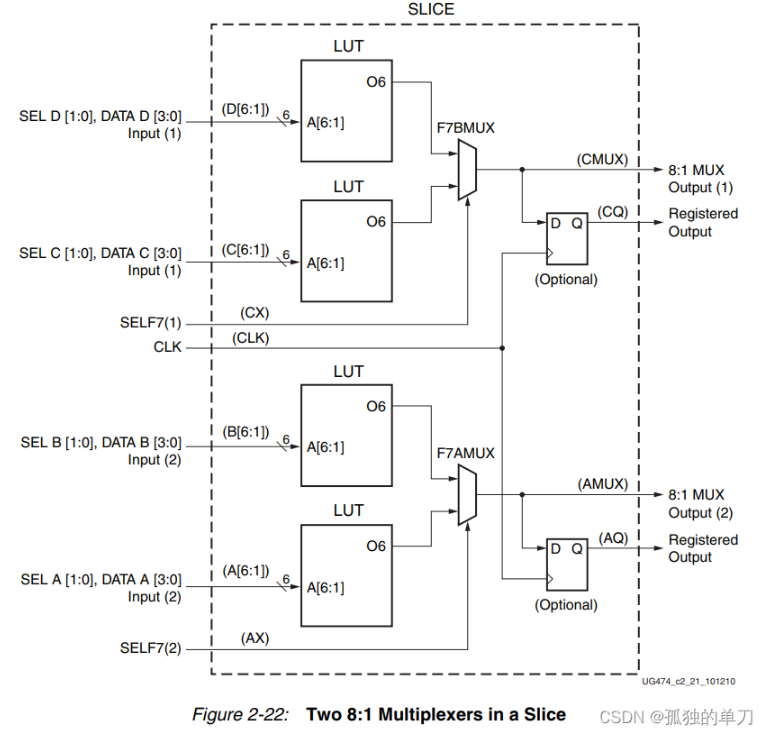

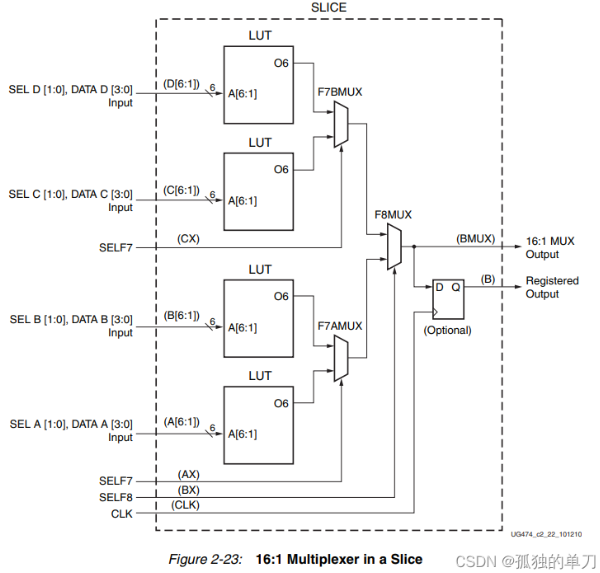

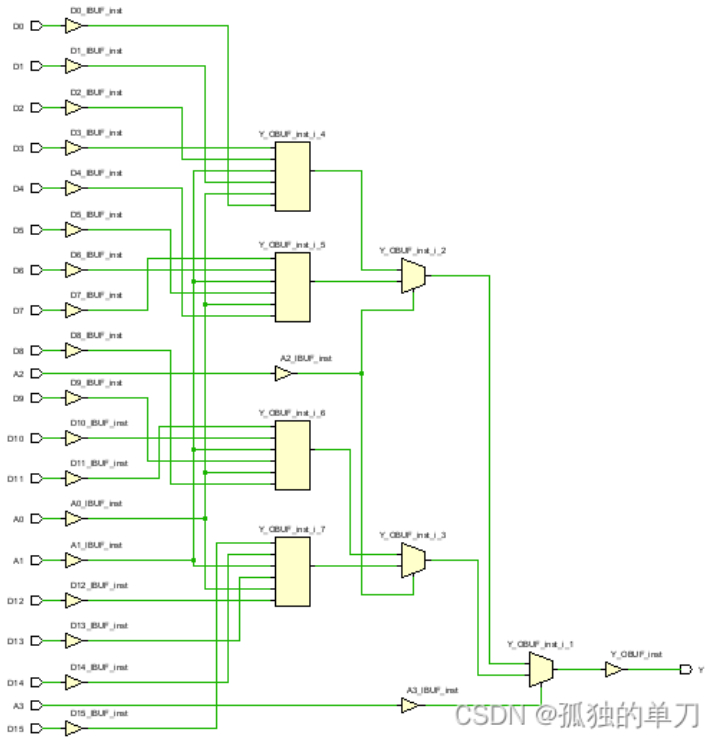

SLICE中的三个MUX(Multiplexer:F7AMUX,F7BMUX和F8MUX)可以和LUT6联合共同实现更大的MUX。事实上,一个LUT6可实现4选1的MUX。

- MUX4的实现使用一个LUT6,其中LUT6的4个输入作为MUX4的4个输入,而另外2个输入则作为MUX4的地址线。

每个SLICE中都有2个MUXF7+1个MUXF8。MUXF7 的输入只能为LUT6的输出,而输出只能接到MUXF8; MUXF8的输入只能为MUXF7的输出

SLICE中的F7MUX(F7AMUX和F7BMUX)的输入数据来自于相邻的两个LUT6的O6端口

MUX4可以由LUT6来实现,每个SLICE可以实现4个独立的MUX4

MUX8可以由2LUT6+1个MUXF7来实现,每个SLICE可以实现2个独立的MUX8

MUX16可以由4个LUT+2个MUXF7+1个MUXF8来实现,每个SLICE可以实现1个独立的MUX16

3.进位链(Carry Chain)

- 进位链用于实现加法和减法运行。就是结构图中,中间那个大的部分,可以看到它内部实际还包含4个MUX和4个2输入异或门(XOR)。异或运算是加法运算中必不可少的运算

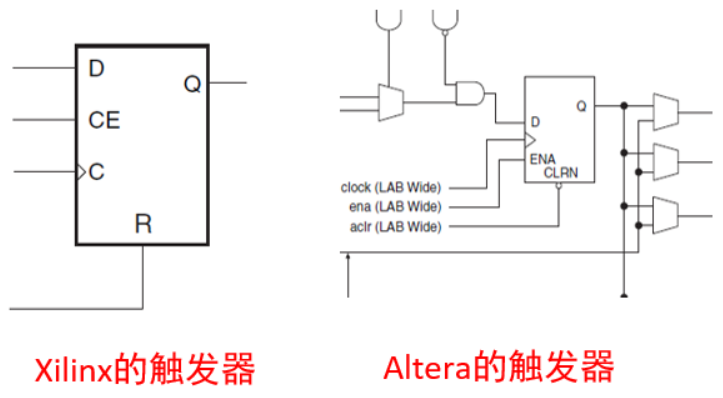

4.触发器

每个SLICE中有8个触发器。这个8个触发器可分为两大类:4个只能配置为边沿敏感的D触发器(Flip-Flop)和4个既可配置为边沿敏感的D触发器又可配置为电平敏感的锁存器(Flop&Latch)。当后者被用作锁存器的时候,前者将无法使用。

Xilinx的触发器是高电平复位,而Altera的触发器时低电平复位

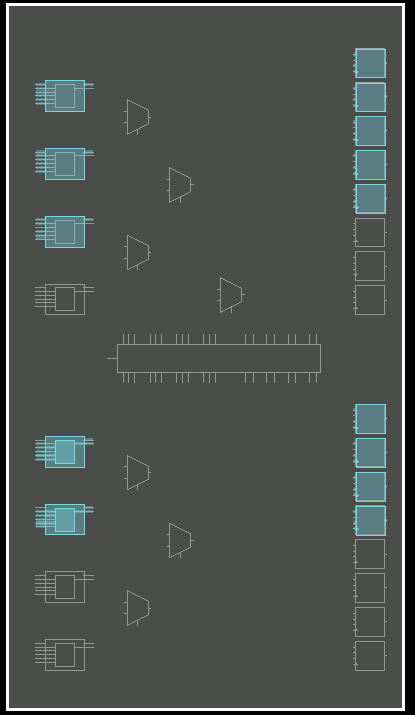

BRAM

- 绝大多数FPGA都具有内嵌的块RAM。BRAM可被配置成位单端口RAM,双端口RAM,内容寻址存储器和FIFO等常用的存储结构。

- 一般的FPGA器件中,单片BRAM的容量为18Kbit,即位宽为18bit、深度为1024,可根据需要改变其位宽和位深也可将多片BRAM级联构成大规模RAM。

DSP

- DSP硬核中的核心资源就是一个高性能的硬件乘法器,外加一些累加器和寄存器、复用器等资源。DSP硬核通过将这些高性能的资源紧密的结合在一起,从而让FPGA芯片具有强大的数字信号处理运算的能力。