本节主要介绍了简单的TMDS连接,并以一个基础的彩条实验测试了RGB2DVI的使用。

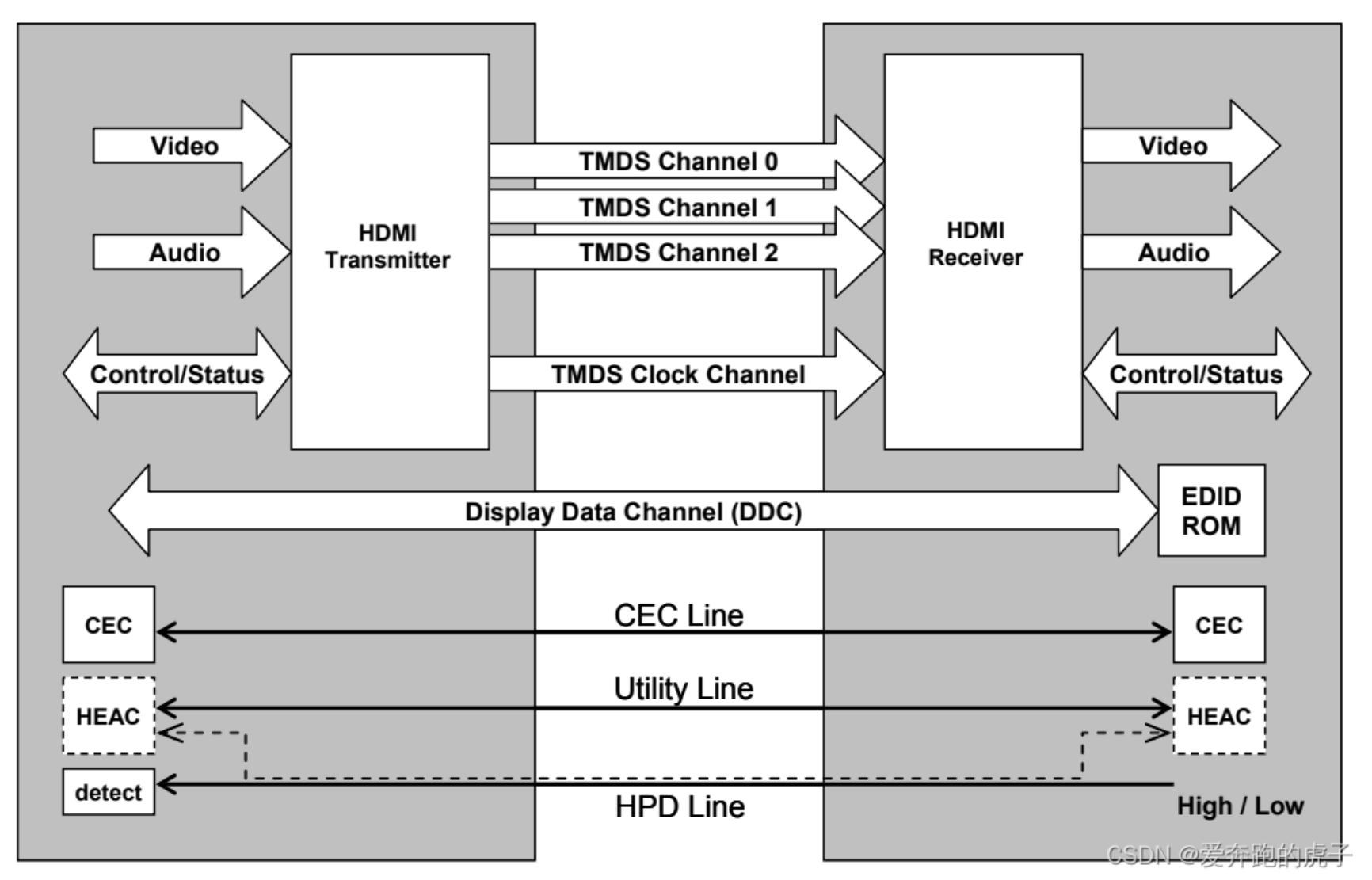

HDMI传输框架

TMDS连接

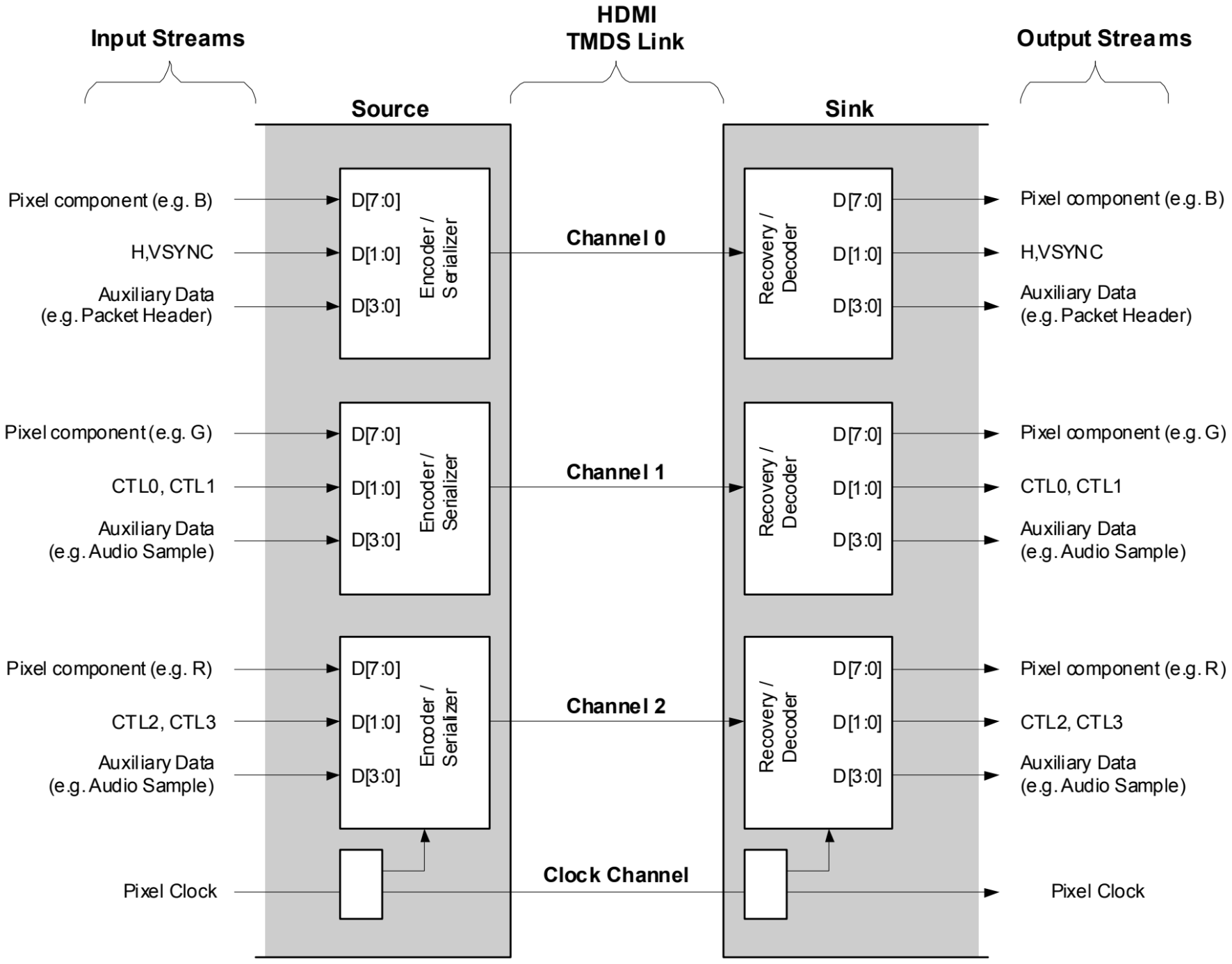

TMDS连接从逻辑功能上可以划分成两个阶段:编码和并串转换。在编码阶段,编码器将视频源中的像素数据、HDMI的音频/附加数据,以及行同步和场同步信号分别编码成10位的字符流。然后在并串转换阶段将上述的字符流转换成串行数据流,并将其从三个差分输出通道发送出去。

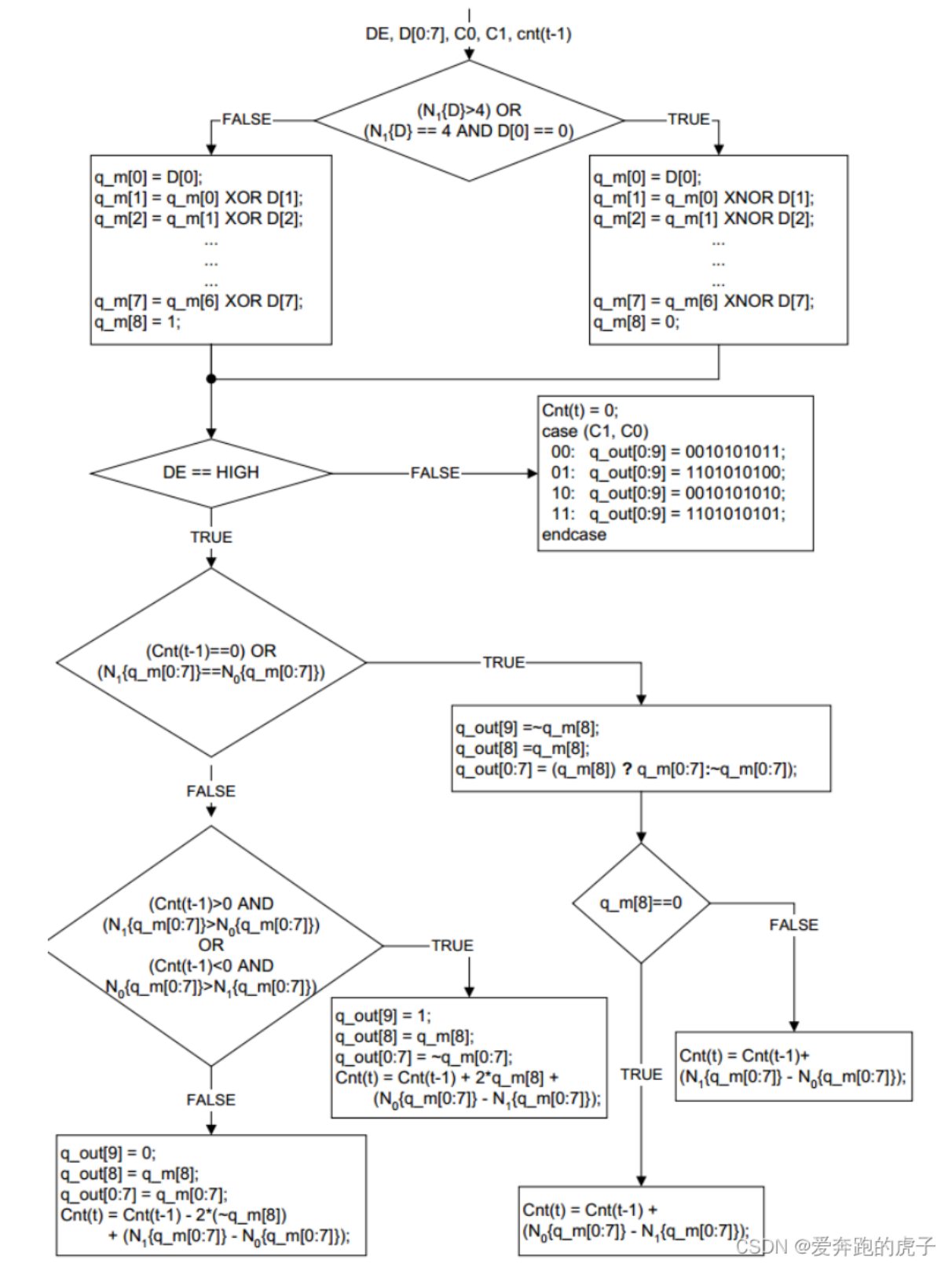

1.TMDS编码

TMDS(Transition Minimized Differential Signaling)是最小化差分传输的简称,实际上就是一种编码规则,主要是适用于HDMI接口、DVI接口的视频图像编码

TMDS编码规则是将8比特的像素数据转换成10比特数据

- 这10比特数据的前8比特是由原始8位像素数据通过异或运算或者同或运算得到

- 如果前8比特采用同或(异或非)运算得到,那么第9比特为0,如果前8比特数据是由原始8比特像素数据通过异或运算得到,那么第9比特为1

- 第10比特是直流平衡位,当转换后的10比特数据中0比较多,那么比特10位为1。如果转化后的数据中1比较多,那么比特10位为0

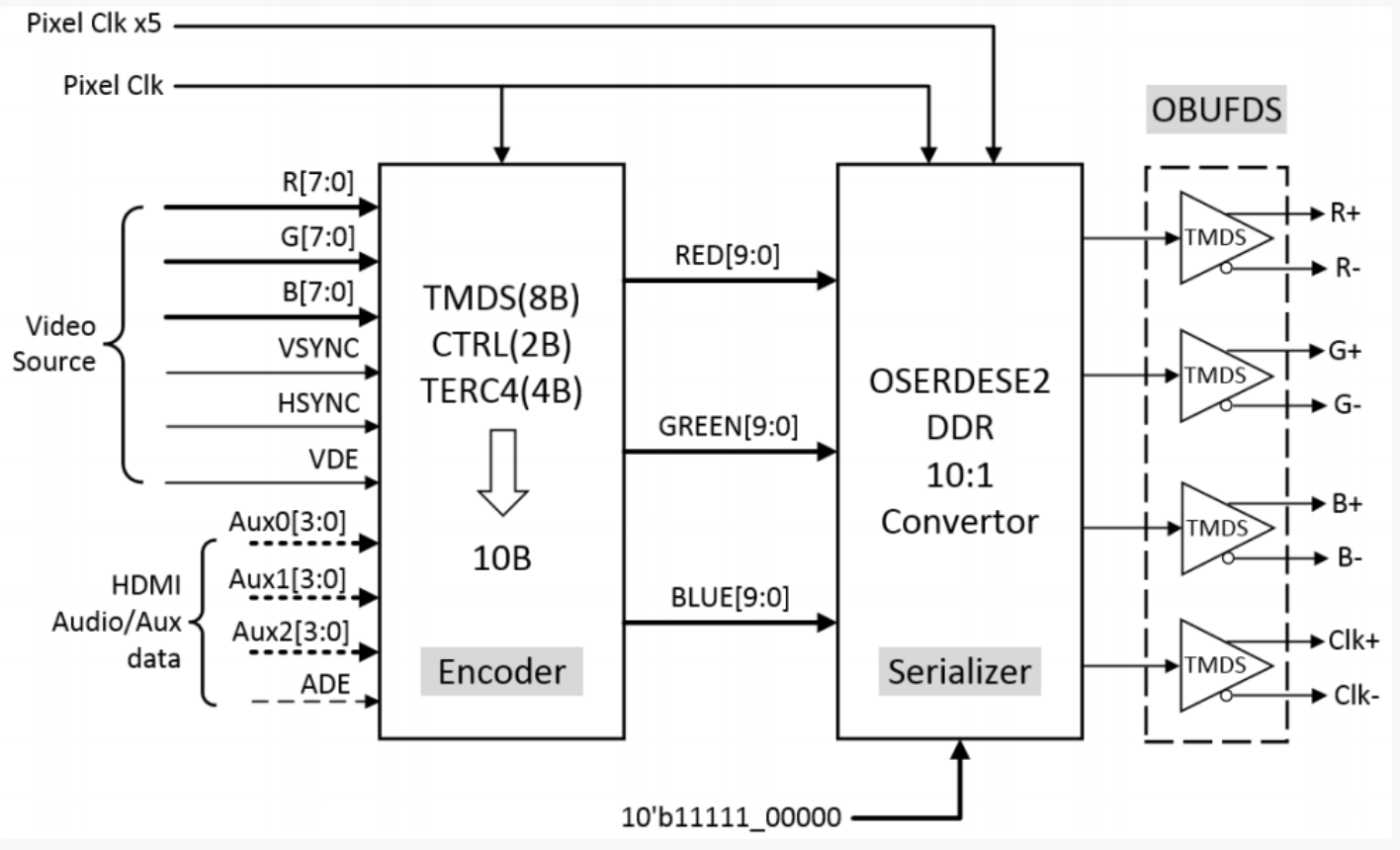

TMDS的编码框图有B、G、R三个通道,这三个通道对应24bit的像素数据,分别为8比特蓝色像素、8比特绿色像素、8比特红色像素(除了要对B、G、R这三个通道的8比特像素数据进行编码,还需要对行、场同步信号进行编码,行、场同步是接到蓝色数据通道的D[1:0]的,行、场同步信号的编码不会经过一系列的异或、同或等逻辑运算),而是直接采用查找表的形式去实现。)

每个数据传输通道还接了一个DE信号,DE信号就是像素数据使能信号。当DE信号拉高时,对每个通道的8比特像素数据进行编码,当DE信号拉低时,在蓝色通道中去对行、场同步信号进行编码,而绿色通道和红色通道一般接控制信号,但在本文没有使用到控制信号,所以绿色通道和红色通道的D[1:0]都给0

TMDS编码流程

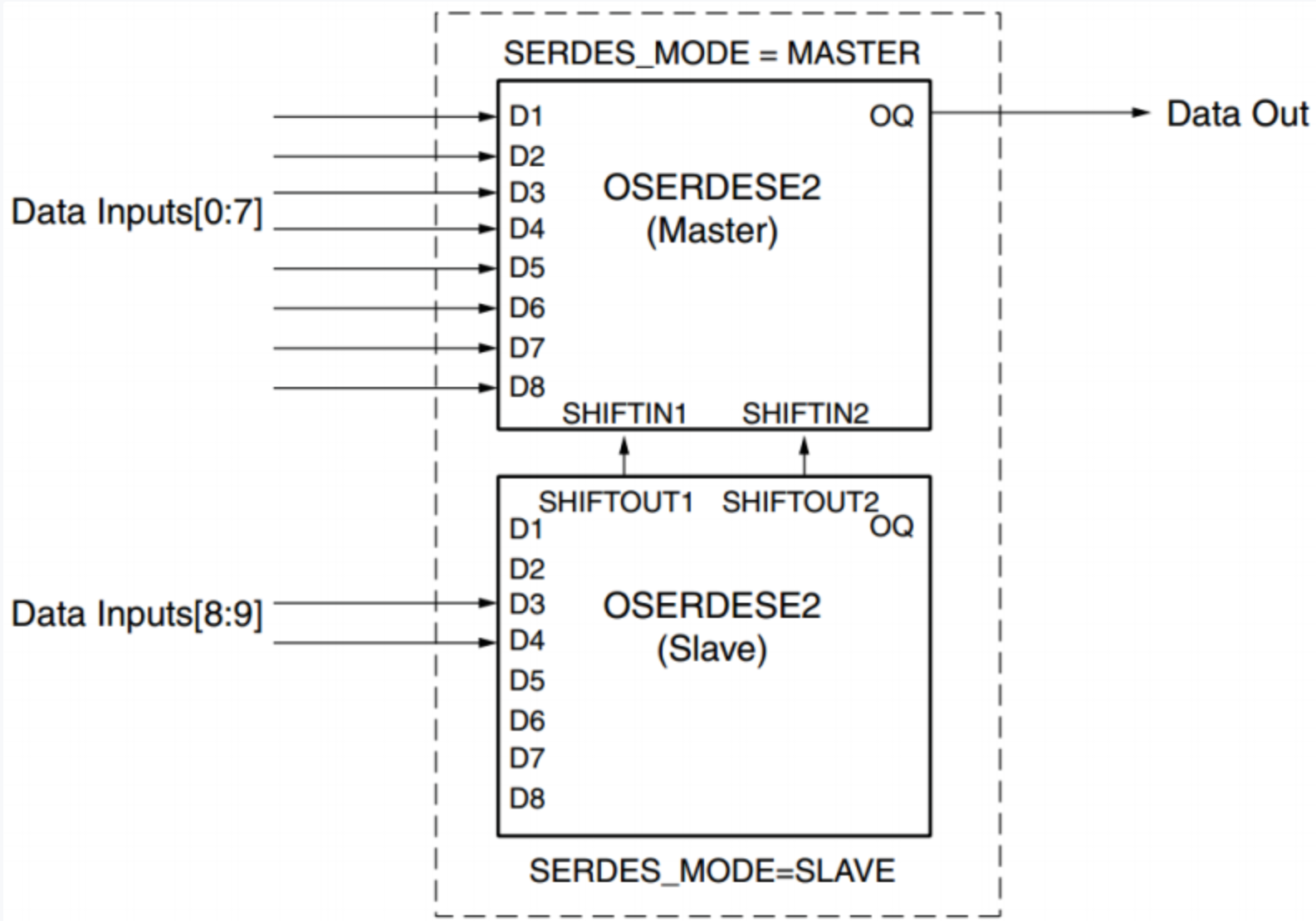

2.TMDS并转串

整个系统需要两个输入时钟,一个是视频的像素时钟 div_clk,另外一个时钟 ser_clk 的频率是像素时钟的五倍。并串转换过程的实现的是 10:1 的转换率,理论上转换器需要一个 10 倍像素频率的时钟。这里我们只需要一个 5 倍的时钟频率,这是因为 OSERDESE2 模块可以实现 DDR 的功能,即它在五倍时钟频率的基础上又实现了双倍数据速率。

DDR(双倍数据速率)概念: DDR技术的核心是利用时钟的上升沿和下降沿来传输数据。换句话说,数据在每个时钟周期的两个边缘(上升沿和下降沿)上都会被采样和传输,从而实现每个时钟周期传输两倍的数据量。

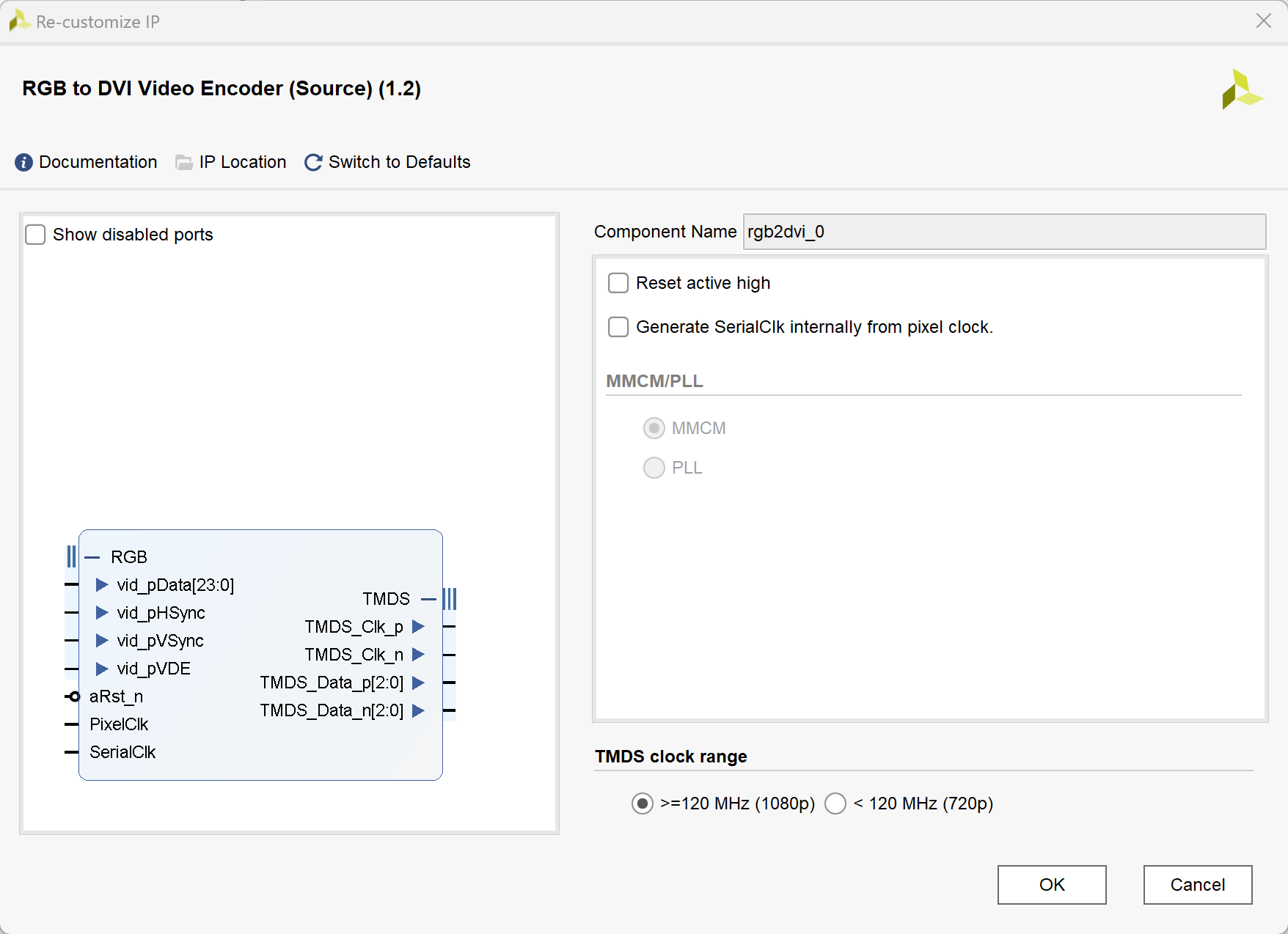

基于RGB2DVI IP核的HDMI彩条实验

RGB2DVI IP核是将RGB数据转化为TMDS信号,这个IP核实际上就是实现了上述TMDS连接对应的功能

参考Reference1,这里就不列举了,直接粘贴结果

PS:不知道是板子原因还是什么原因,得接网线才能会不闪屏,不然会闪屏