本节主要介绍了突发长度下FIFO深度的计算方法。

burst length相关

- 假设模块A不间断地往FIFO中写数据,模块B同样不间断地从FIFO中读数据,不同的是模块A写数据的时钟频率要大于模块B读数据的时钟频率,那么那些没有被读走的数据会越积累越多,那么FIFO深度需要是无穷大的,因此只有在突发数据传输过程中讨论FIFO深度才是有意义的。

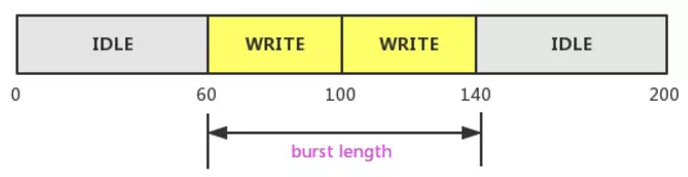

- 连续不断传递完一包数据,歇会,再接着传下一包数据,在每段连续传输时间内传递的数据个数称为burst length

- 要确定FIFO的深度,关键在于计算出在突发读写这段时间内有多少个数据没有被读走,也就是说FIFO的最小深度就等于没有被读走的数据个数

FIFO深度计算的常见场景

- 假设模块A向FIFO写数据的时钟频率为$f_a$,模块B从FIFO读数据的时钟频率为$f_b$

1.写速率$fa$ > 读速率$f_b$

- 场景一:$f_a>f_b$,burst读写期间没有空闲周期

- 写数据时钟频率fa=80MHz,读数据时钟频率fb=50MHz,突发长度=120。在突发传输过程中,数据都是连续读写的。

- 那么:

- 突发写入120个数据的时间为:$120\times(\frac1{80MHz})=1500ns$

- 而在1500ns内,可以读到的数据个数是:$1500\div(\frac1{50MHz})=75$

- 那么FIFO的深度为:$120-75 = 45$(那在读数据模块在读取fifo中这45个数时,写模块就该一直休息了,等读模块读完才可进行下一次突发传输)

- 场景二:$f_a>f_b$,burst读写期间有空间周期

- 写数据时钟频率fa=80MHz,读数据时钟频率fb=50MHz,突发长度=120。每隔1个cycle写一次,每隔3个cycle读一次

- 那么:

- 每隔1clk才写一次,就意味着实际上写频率为$f_a/2$;每隔3clk才读一次,就意味着实际上读频率为$f_a/4$

- 突发写入120个数据的时间为:$120\times(\frac1{80/2MHz})=3000ns$

- 而在3000ns内,可以读到的数据个数是:$3000\div(\frac1{50/4MHz})=37.5$

- 那么FIFO的深度为:$120-37.5 = 82.5$。因此FIFO的最小深度为83

- 场景三:$f_a>f_b$,burst读写期间读写使能有空闲,此场景情况与场景二的计算方式一致

- 写数据时钟频率fa=80MHz,读数据时钟频率fb=50MHz,突发长度=120,写使能信号占整个burst时间比重为1/2,读使能信号占整个burst时间比重为1/4

- 那么:

- 与场景二类似,写使能信号占整个burst时间比重为1/2,就意味着实际上写频率为$f_a/2$;读使能信号占整个burst时间比重为1/4,就意味着实际上读频率为$f_a/4$

- 因此,FIFO的最小深度为83

2.写速率$f_a$< 读速率$f_b$

- 场景一:$f_a<f_b$,burst读写期间没有空闲周期

- 写数据时钟频率fa=40MHz,读数据时钟频率fb=50MHz,突发长度=120,在突发传输过程中,数据都是连续读写的

- 那么:

- 由于读比写快,并没有数据会因为读不完而需要fifo缓存,故FIFO只起到过时钟域的作用,FIFO的最小深度为1即可

- 场景二:$f_a<f_b$,burst读写期间有空间周期

- 写数据时钟频率fa=40MHz,读数据时钟频率fb=50MHz,突发长度=120,每隔1个cycle写一次,每隔3个cycle读一次

- 那么:

- 突发写入120个数据的时间为:$120\times(\frac1{40/2MHz})=6000ns$

- 而在6000ns内,可以读到的数据个数是:$6000\div(\frac1{50/4MHz})=75$

- 那么FIFO的深度为:$120-75 = 45$

3.写速率$f_a$= 读速率$f_b$

- 场景一:$f_a=f_b$,burst读写期间没有空闲周期

- 写数据时钟频率fa=50MHz,读数据时钟频率fb=50MHz,突发长度=120

- 那么:

- 如果读写时钟同源并且无相位差,那么可以不需要FIFO;否则FIFO的最小深度为1

- 场景二:$f_a=f_b$,burst读写期间有空闲周期

- 写数据时钟频率fa=50MHz,读数据时钟频率fb=50MHz,突发长度=120,每隔1个cycle写一次,每隔3个cycle读一次

- 那么:

- 突发写入120个数据的时间为:$120\times(\frac1{50/2MHz})=4800ns$

- 而在4800ns内,可以读到的数据个数是:$4800\div(\frac1{50/4MHz})=60$

- 那么FIFO的深度为:$120-60 = 60$

4.读写使能随机

写数据时钟频率fa=80MHz,读数据时钟频率fb=50MHz,在写时钟周期内,每100个周期就有40个数据写入FIFO,在读时钟周期内,每10个周期可以有8个数据读出FIFO

在最坏的情形中,读写的速率应该相差最大,也就是说需要找出最大的写速率和最小的读速率

只有在背对背情况下写速率才是最高的

写数据时钟频率fa=80MHz,读数据时钟频率fb=50MHz,在写时钟周期内,每100个周期就有40个数据写入FIFO,在读时钟周期内,每10个周期可以有8个数据读出FIFO。

那么:

- 在背对背情形下,相当于burst length为80

- 突发写入80个数据的时间为:$80\times(\frac{1}{80MHz})=1000ns$

- 而在1000ns内,读出的数据为:$1000\div (10\times\frac{1}{50MHz}) \times 8=40$

- 那么FIFO的深度为:$80-40 = 40$

- 而读模块读fifo中数据花费的时间为:$(40\div 8 )\times(10\times\frac{1}{50MHz})=1000ns$

- 而写模块中的idle时间为:$120\times(\frac{1}{80MHz}) = 1500ns$

- 由于1500ns>1000ns,读模块完全可以在写模块空闲的这段时间内将数据读完,故该答案成立