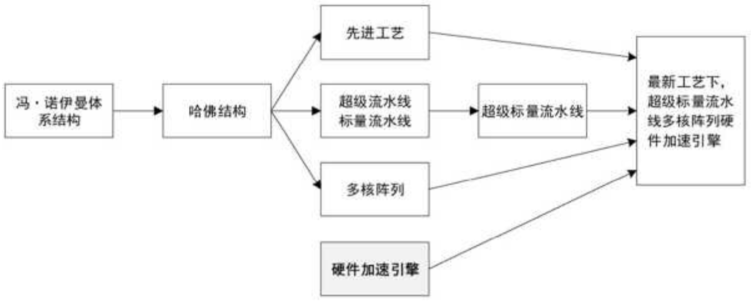

本节主要介绍了FPGA图像处理的准备知识,包括什么是硬件加速引擎?如何用脚本的方式运行modelsim?

CPU体系结构简介

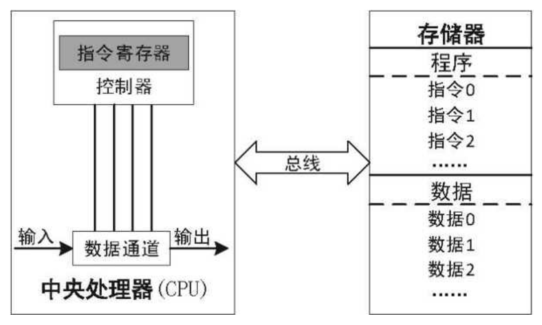

冯诺依曼体系结构CPU,是一种将程序指令和数据合并在一起的存储器结构。该结构中程序指令和数据共用一条总线,通过时分复用的方式进行读写操作,结构相对简单,总线面积较小,但缺点是效率低,无法同时取程序指令和数据,成为执行的瓶颈。

哈佛结构是一种将程序指令和数据分开的存储器结构。该结构由于程序指令和数据存储在两个独立的存储器,各自有独立的访问总线,因此提供了更大的存储器带宽,减轻了程序运行时访问内存的瓶颈。但相应的也需要独立的存储器,以及更大的总线面积。

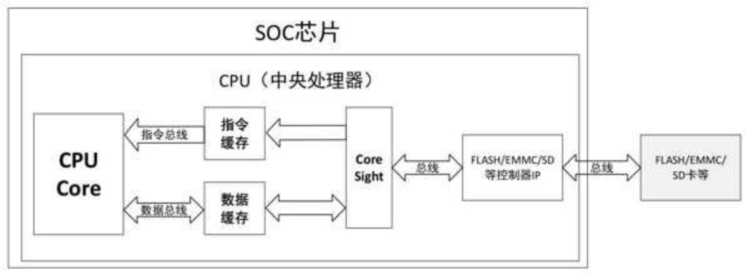

改进的哈佛结构,指令和数据还是一起存储在主存储器中,但CPU有额外的指令存储器和数据存储器。在主存储器带宽足够的前提下,使CPU可以同时取指令和数据

什么是硬件加速引擎

如果将某些复杂耗时的计算,采用专用芯片实现,完成计算后,将结果返回给CPU,这样就实现了专用的加速引擎。

硬件加速引擎也称为硬件加速器,其原理是采用专用的加速芯片/模块,替换CPU完成复杂耗时的大算力操作,其过程不需要或者仅少量需要CPU的参与。

典型的硬件加速引擎有GPU(图形运算单元)、DSP、ISP(图像信号处理器)、NPU(神经网络处理器)

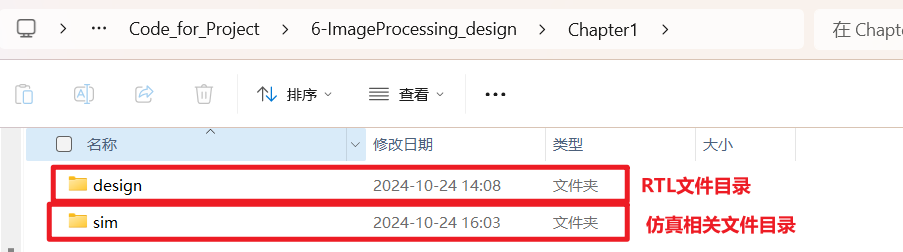

FPGA软件仿真环境介绍

1.filelist常见写法

+define+<define_name>- 相当于在filelist.f中的每个文件都加入了`define define_name

+incdir+<dir_path>- filelist中每个文件中的include都会在dir_path路径下搜索

库文件的搜索

添加某个目录下的多个文件到库文件(告诉工具在指定的目录下搜索以

.v为扩展名的 Verilog 文件)1

-y /home/yuxiang/proj/sim_libs/unisims+libext+.v

添加一个文件中的多个module到库文件

1

-v /home/yuxiang/proj/tsmc_lib/tsmc13.v

2.do脚本

1 | #run.do文件中#代表注释 |

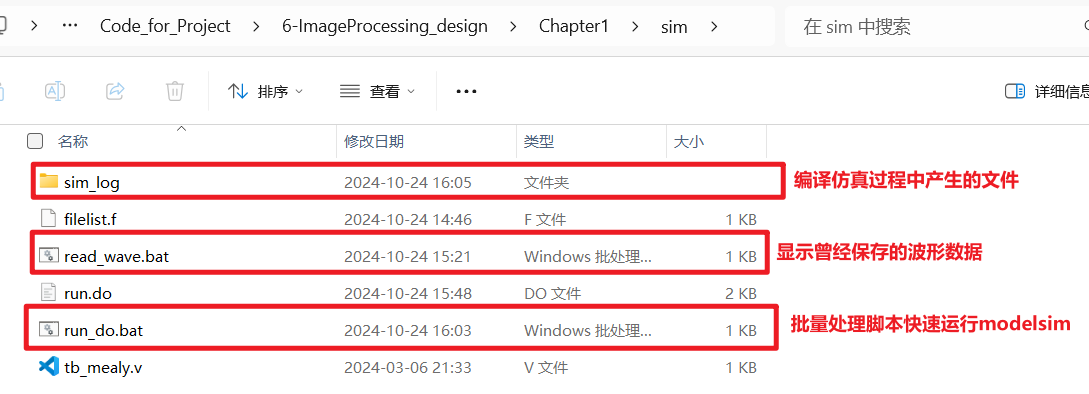

仿真平台文件架构:

run.do文件中要注意:因为run_do.bat中把路径切换至sim_log,所以在run.do中用到文件路径的地方,记得当前是在sim_log目录下的。

2.批量处理脚本

run_do.bat

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23@echo off

title %cd%

if exist sim_log (

rem 删除所有子文件夹

for /d %%d in (sim_log\*) do (

rd /s /q "%%d"

)

rem 删除除了以.wlf和.do为后缀以外的文件

for %%f in (sim_log\*) do (

if /I not "%%~xf"==".wlf" if /I not "%%~xf"==".do" (

del /q "%%f"

)

)

) else (

rem 如果需要重新创建 sim_log 文件夹

md sim_log

)

cd ./sim_log

vsim -do ../run.doread_wave.bat

1

2

3

4@echo off

title %cd%

cd ./sim_log

vsim -view vsim2.wlf -do wave.do

Reference

- 《基于MATLAB与FPGA的图像处理教程》图书及其配套资料