本节主要分享在github中阅读学习别人开源代码的感悟。

https://github.com/omarelhedaby/CNN-FPGA

该代码展开得很少,更多得考虑资源,架构上没有啥特色,就是乘加运算的堆叠【浮点乘加】

但其提供的设计文档很详细

不建议细看

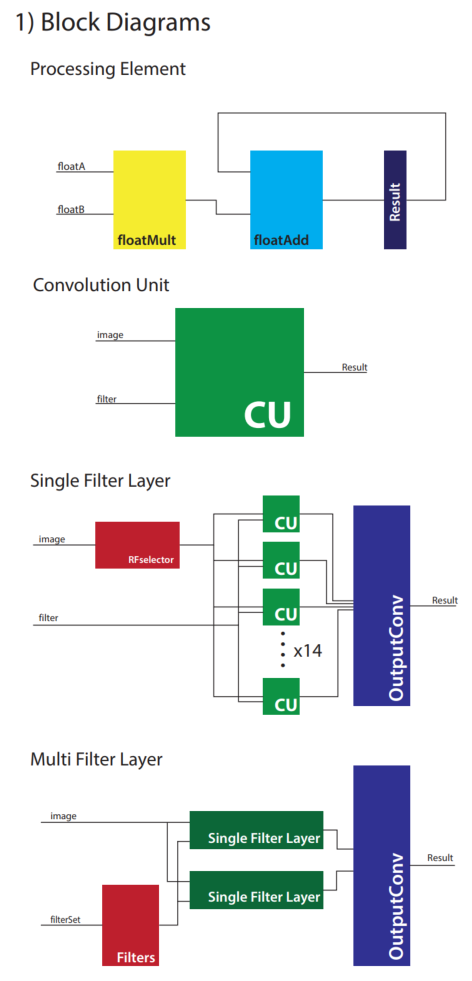

卷积模块设计框图:

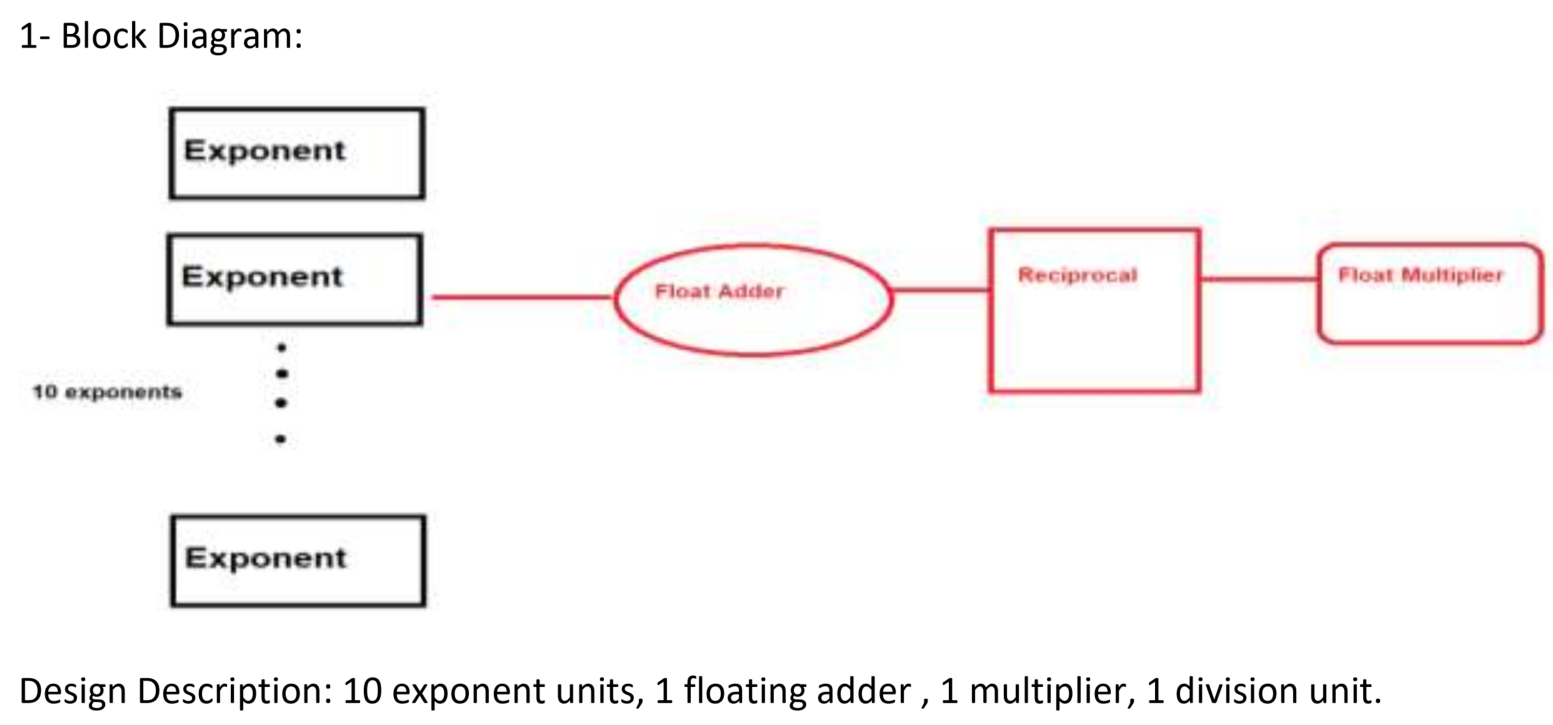

softmax模块设计框图:

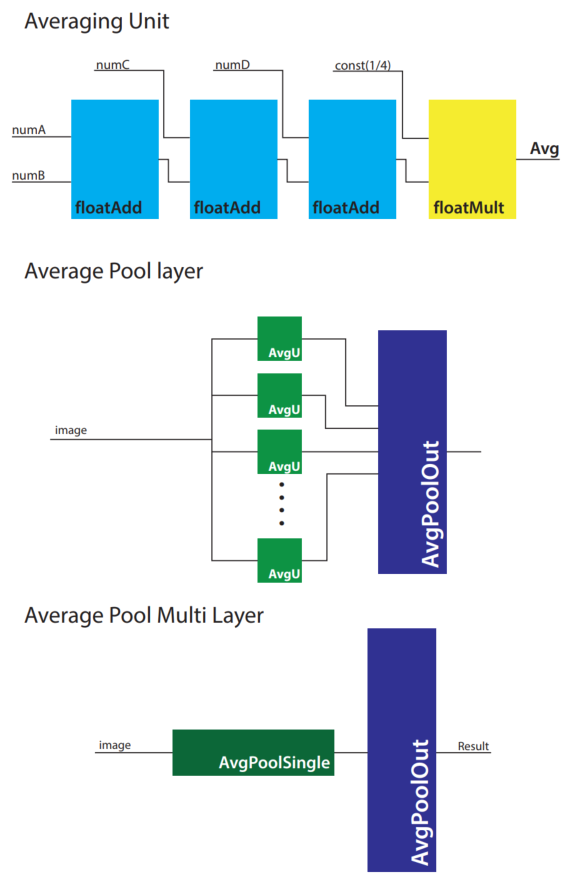

平均池化设计框图:

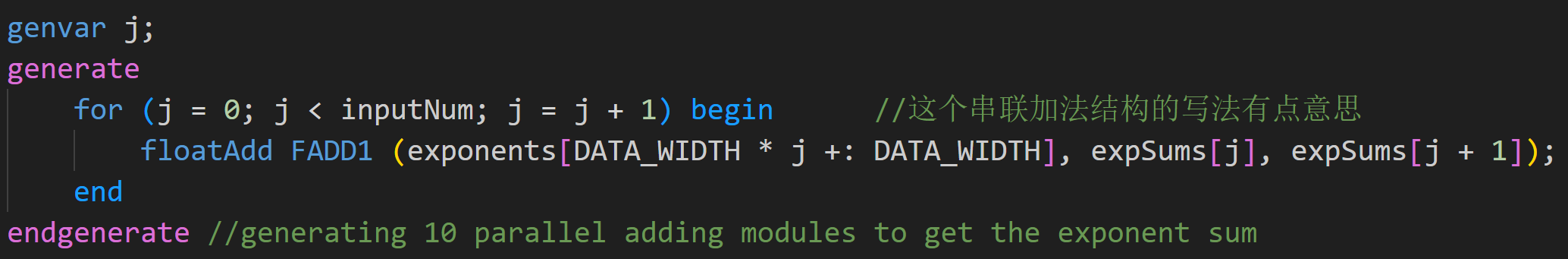

这里面有个串行加法器的写法有点意思:

https://github.com/padhi499/Image-Classification-using-CNN-on-FPGA

该代码主要实现的卷积+ReLu+最大池化,卷积最底层小模块没展开,用串行实现的,但顶层模块均展开并行处理

但总的来说,在整体架构上没有创新特色,就是简单地复制几倍资源并行去做

不建议细看

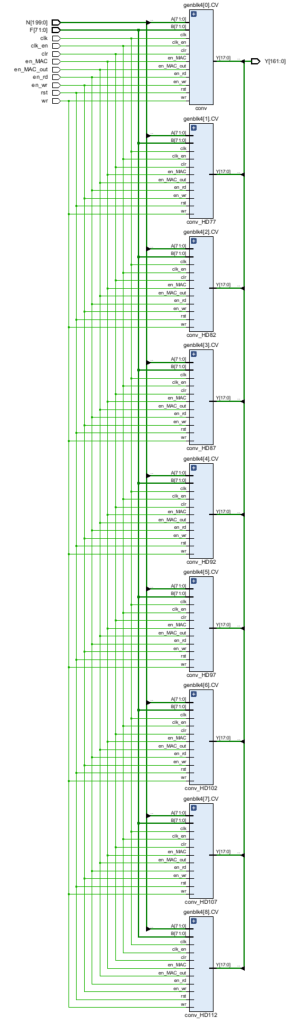

卷积实现框图:

卷积顶层:是9个卷积块的并行(对于$5\times 5$的图片,卷积核是$3\times 3$,步长为1的情况下需要滑动卷积9次,展开后即用9个卷积块并行处理)

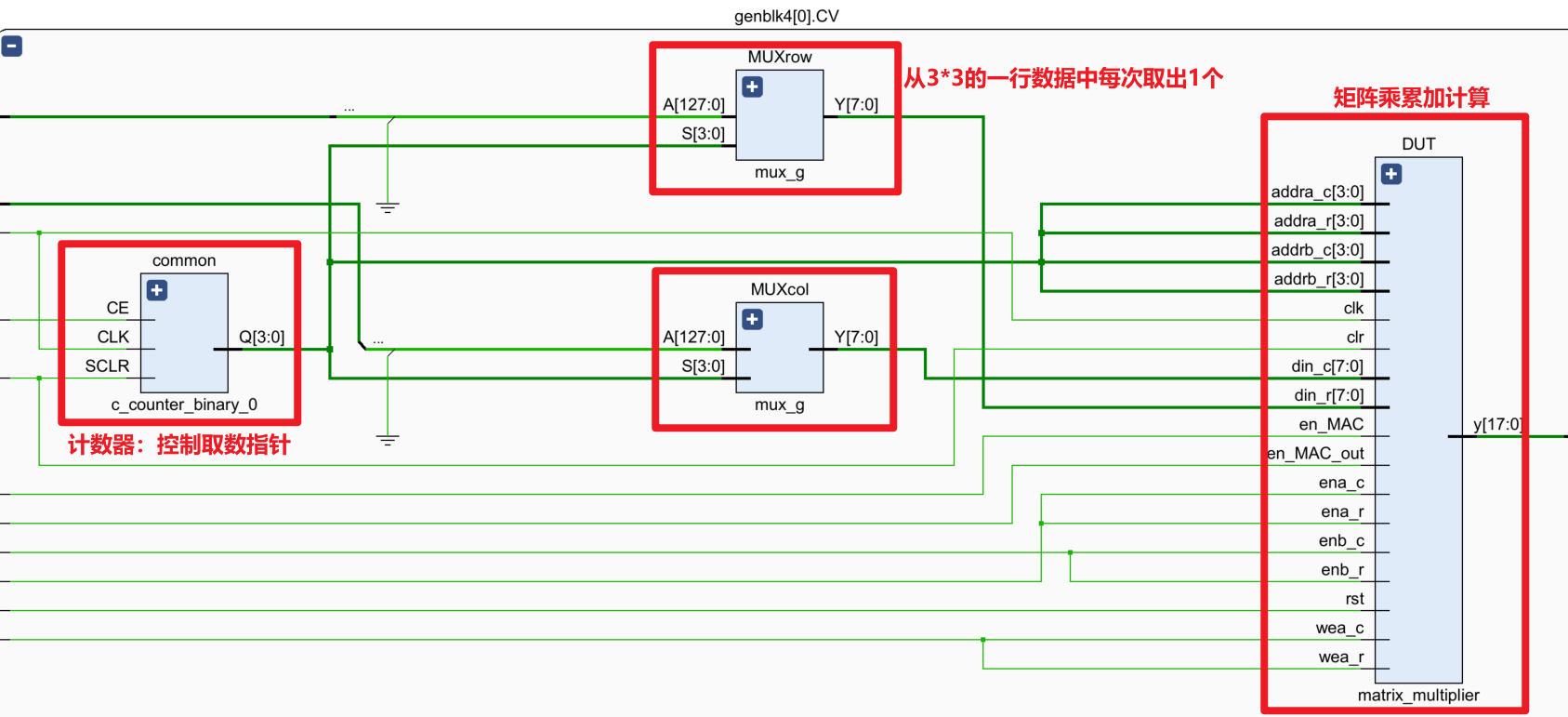

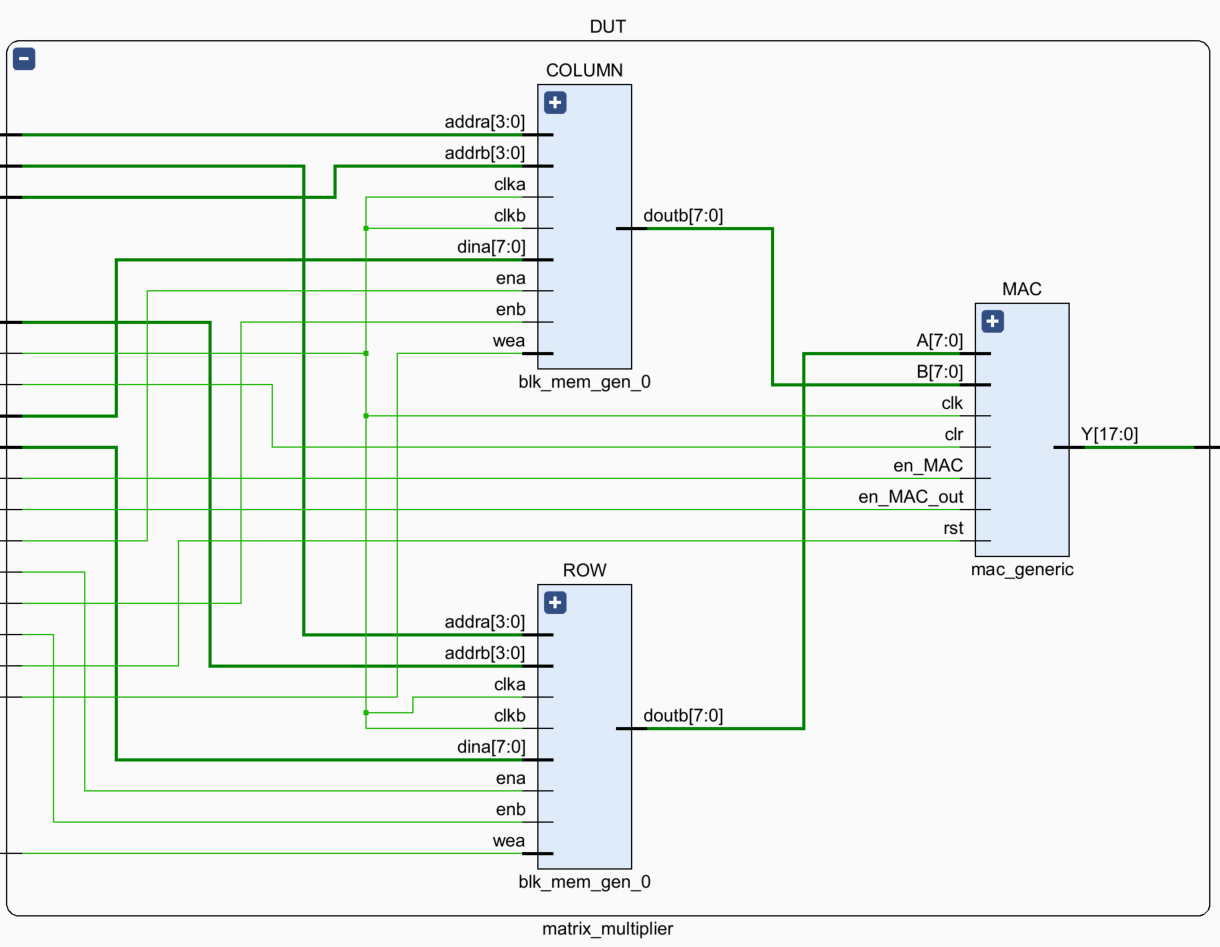

卷积块:

矩阵乘累加模块:这里MAC是串行实现方式,只有一个硬件单元,用时间换资源了

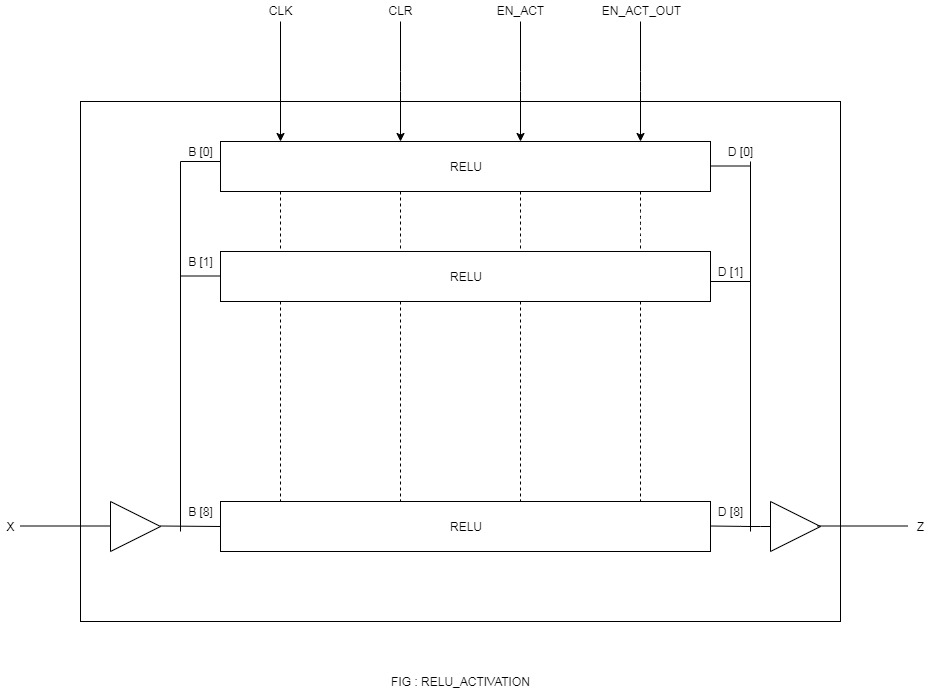

ReLu层:并行Relu

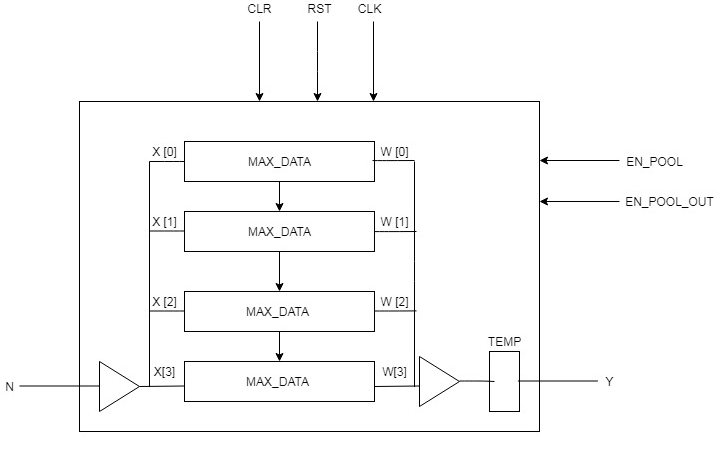

最大池化层:

池化顶层:3 3 经过2 2池化,需要滑动4次池化窗口,故此处为4次展开并行处理

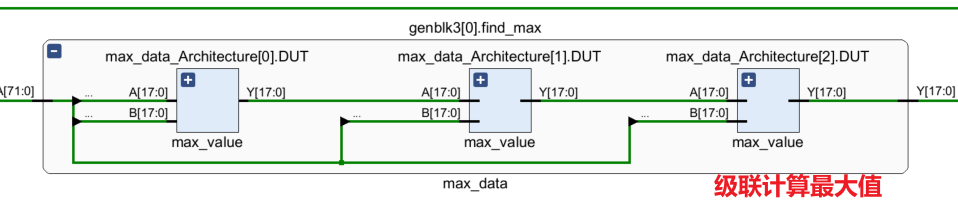

小池化块:对于每次池化窗口22=4个数据,级联方式需要3个比较器得最大值,*这样子可以实现流水处理方式