1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

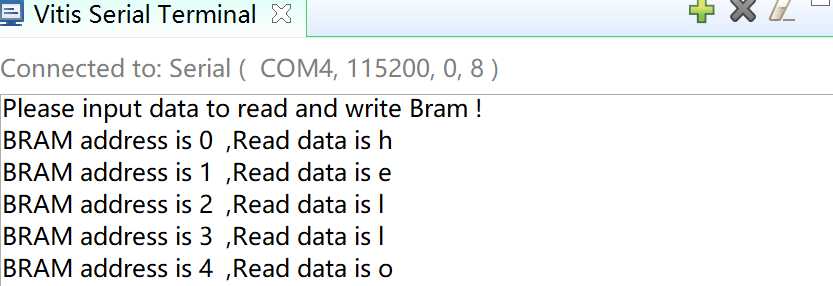

| #include<iostream>

#include<xbram_hw.h>

#include<pl_bram_rd.h>

using namespace std;

#define PL_BRAM_START PL_BRAM_RD_S00_AXI_SLV_REG0_OFFSET

#define PL_BRAM_START_ADDR PL_BRAM_RD_S00_AXI_SLV_REG1_OFFSET

#define PL_BRAM_LEN PL_BRAM_RD_S00_AXI_SLV_REG2_OFFSET

#define PL_BRAM_BASE XPAR_PL_BRAM_RD_0_S00_AXI_BASEADDR

#define START_ADDR 0

#define BRAM_DATA_BYTE 4

char ch_data[1024];

int ch_data_len;

int main()

{

while(1)

{

int i = 0;

int wr_cnt = 0;

int read_data = 0;

printf("Please input data to read and write Bram !\n");

scanf("%s",ch_data);

ch_data_len = strlen(ch_data);

for(i = START_ADDR*BRAM_DATA_BYTE; i<(START_ADDR + ch_data_len)*BRAM_DATA_BYTE; i+=BRAM_DATA_BYTE)

{

XBram_WriteReg(XPAR_BRAM_0_BASEADDR,i,ch_data[wr_cnt]);

wr_cnt++;

}

PL_BRAM_RD_mWriteReg(PL_BRAM_BASE,PL_BRAM_START_ADDR,START_ADDR*BRAM_DATA_BYTE);

PL_BRAM_RD_mWriteReg(PL_BRAM_BASE,PL_BRAM_LEN,ch_data_len*BRAM_DATA_BYTE);

PL_BRAM_RD_mWriteReg(PL_BRAM_BASE,PL_BRAM_START,1);

PL_BRAM_RD_mWriteReg(PL_BRAM_BASE,PL_BRAM_START,0);

for(i = START_ADDR*BRAM_DATA_BYTE; i<(START_ADDR + ch_data_len)*BRAM_DATA_BYTE; i+=BRAM_DATA_BYTE)

{

read_data = XBram_ReadReg(XPAR_BRAM_0_BASEADDR,i);

printf("BRAM address is %d\t,Read data is %c\n",i/BRAM_DATA_BYTE,read_data);

}

}

}

|