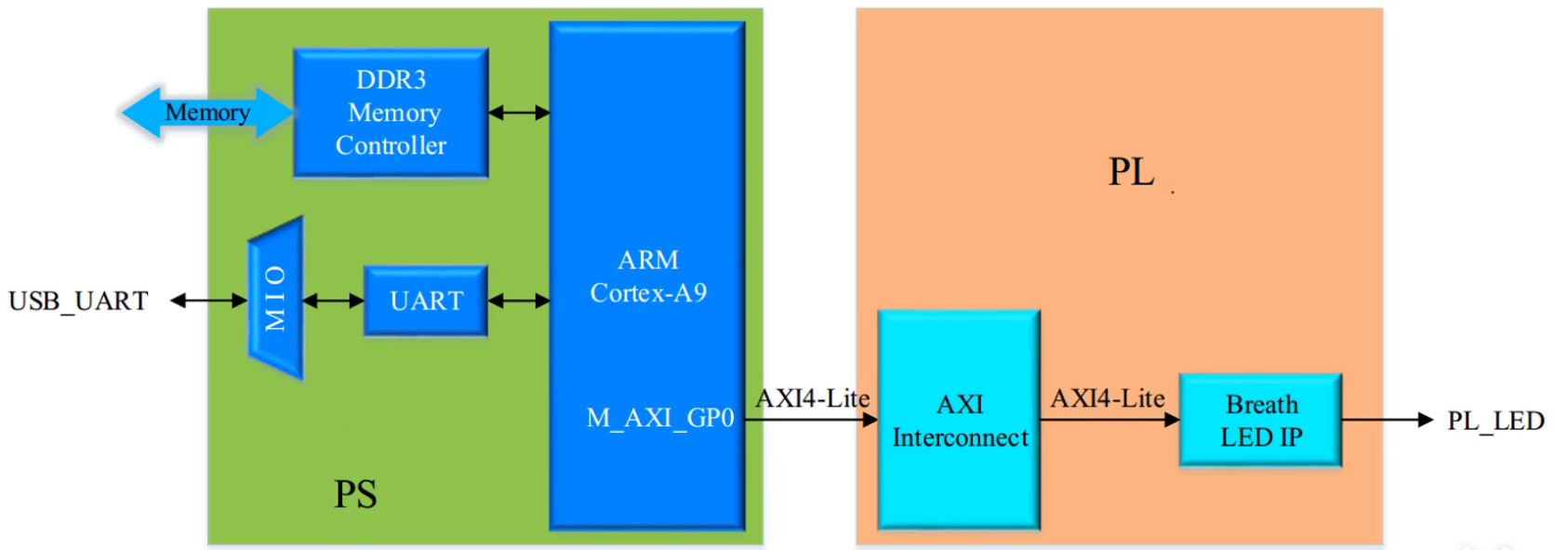

本节主要介绍了Vivado中自定义IP核的创建,以及IP核如何与PS建立联系,并以一个呼吸灯实验为例作为演示

自定义IP核的创建与编辑

1.IP核的创建

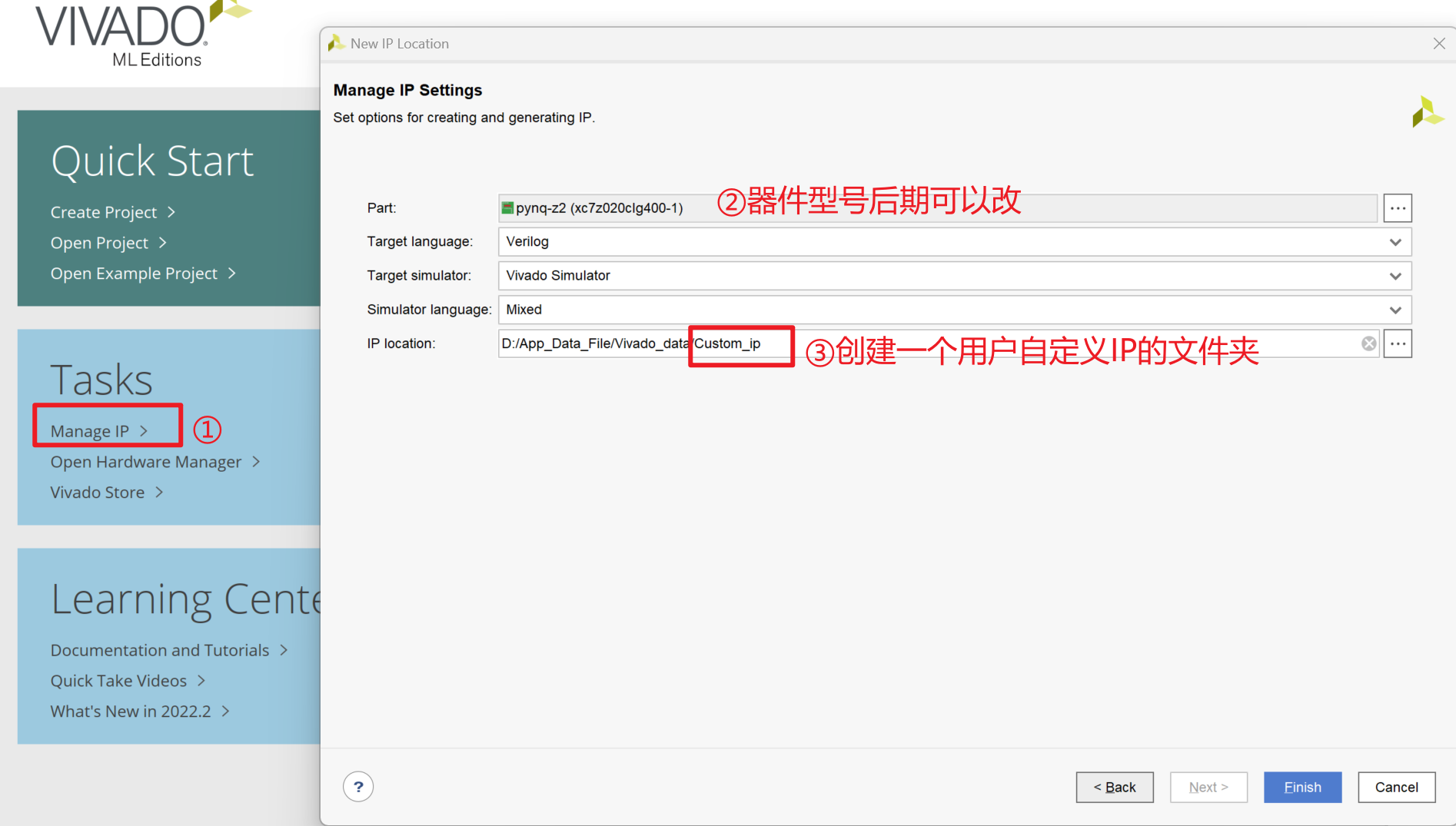

创建管理IP核的工程

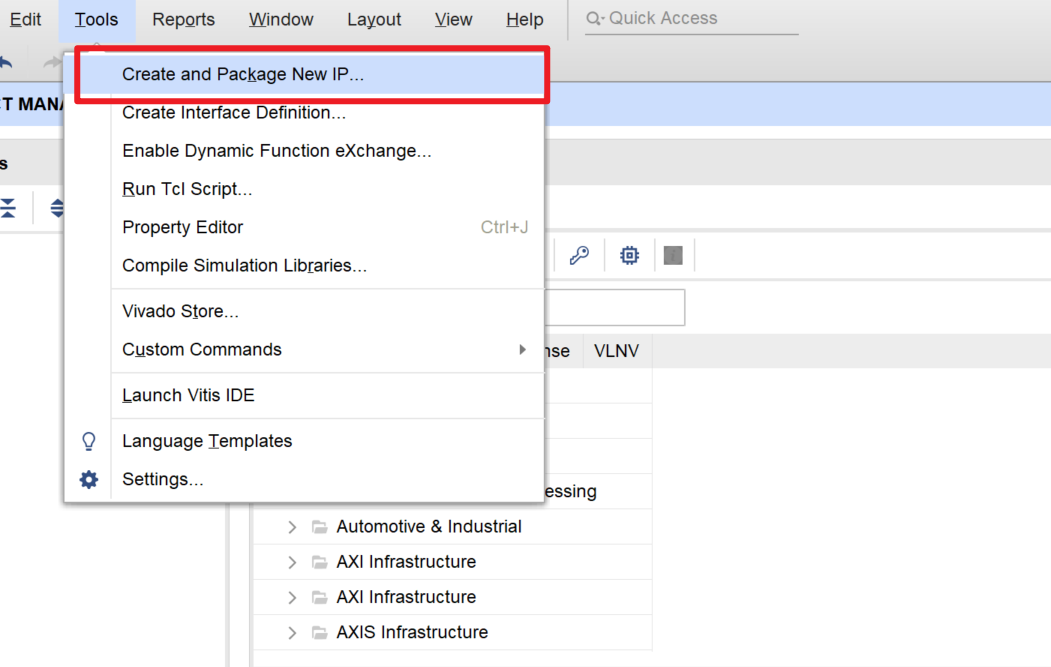

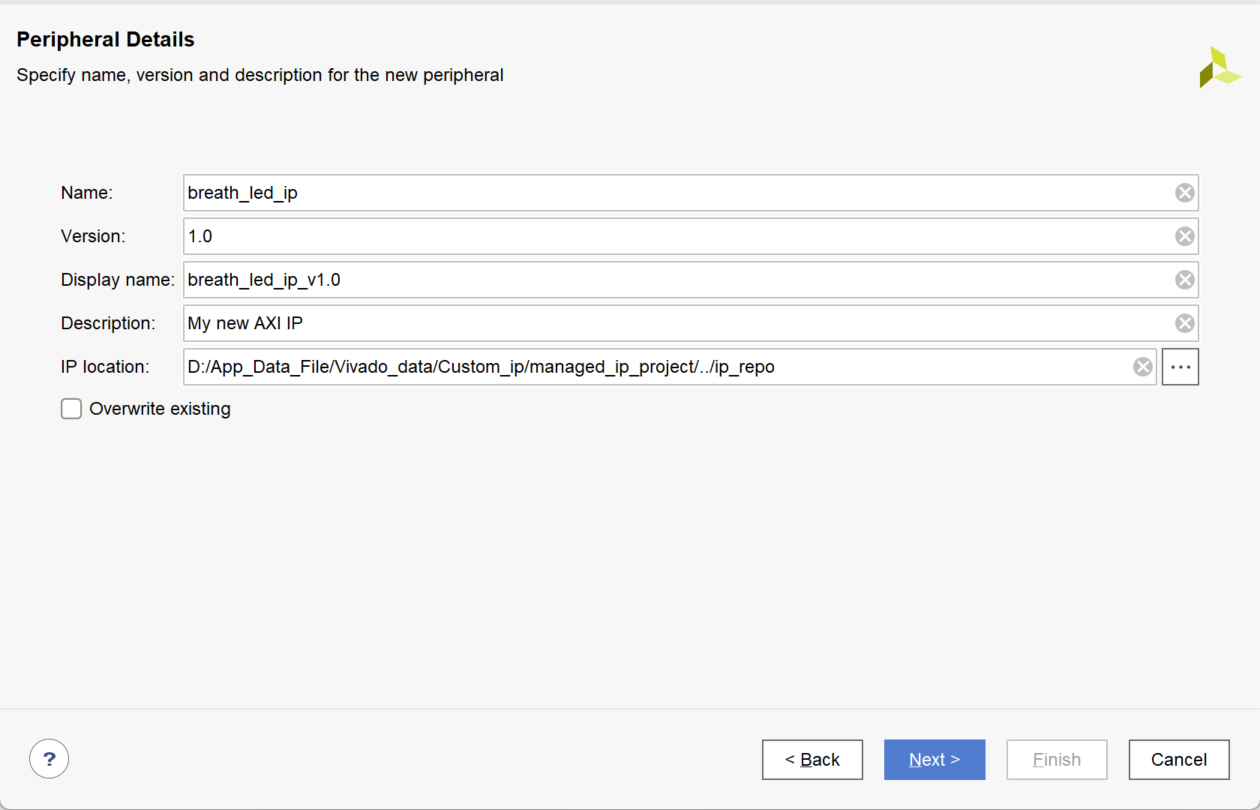

创建并封装一个新的ip

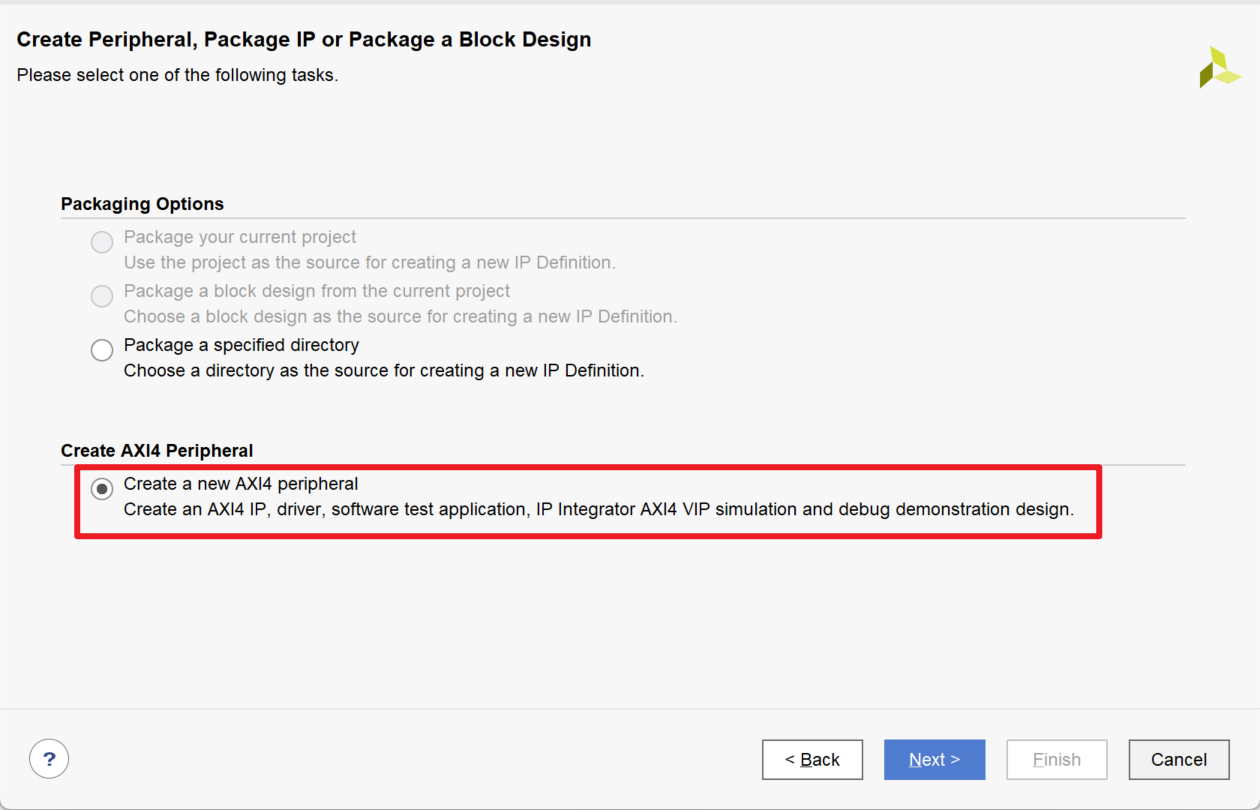

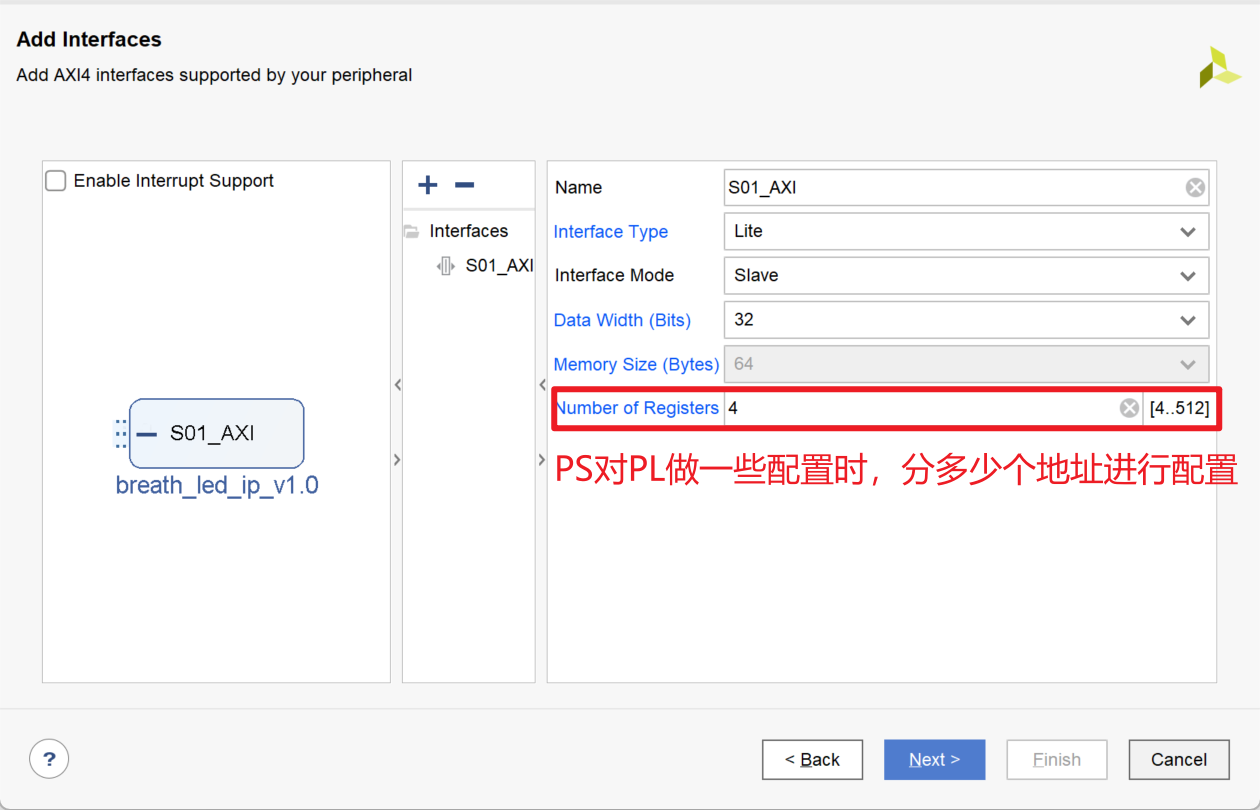

创建AXI4外设:当verilog代码需要跟PS做一些数据交互的时候选这个

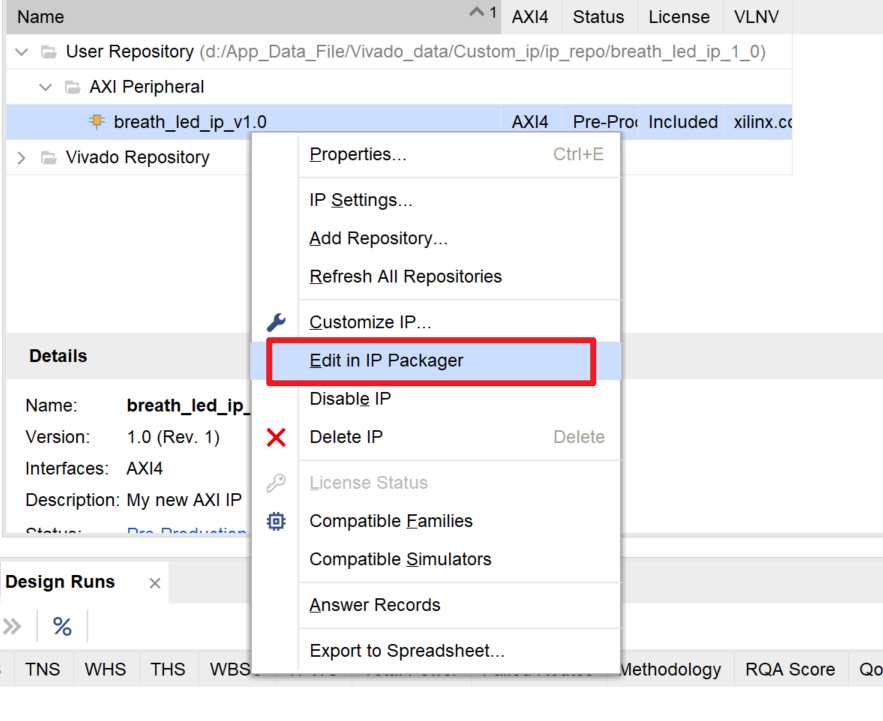

2.IP核的编辑

在IP的封装包内对其进行编辑

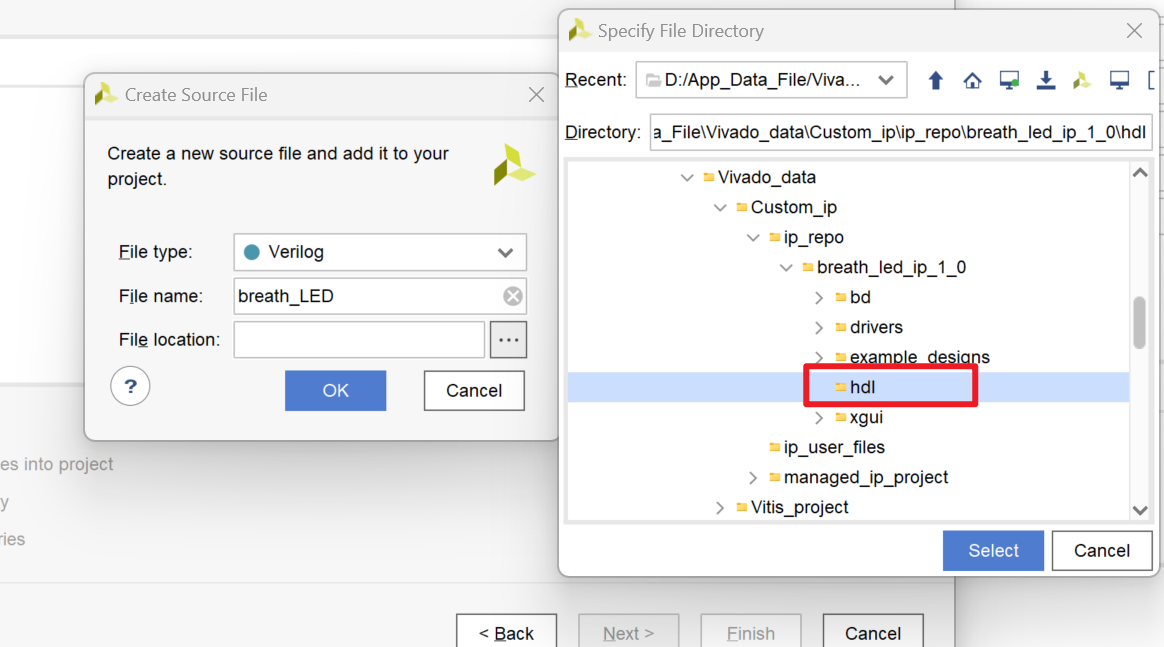

创建breath_LED的verilog设计文件并将其保存在对应目录下

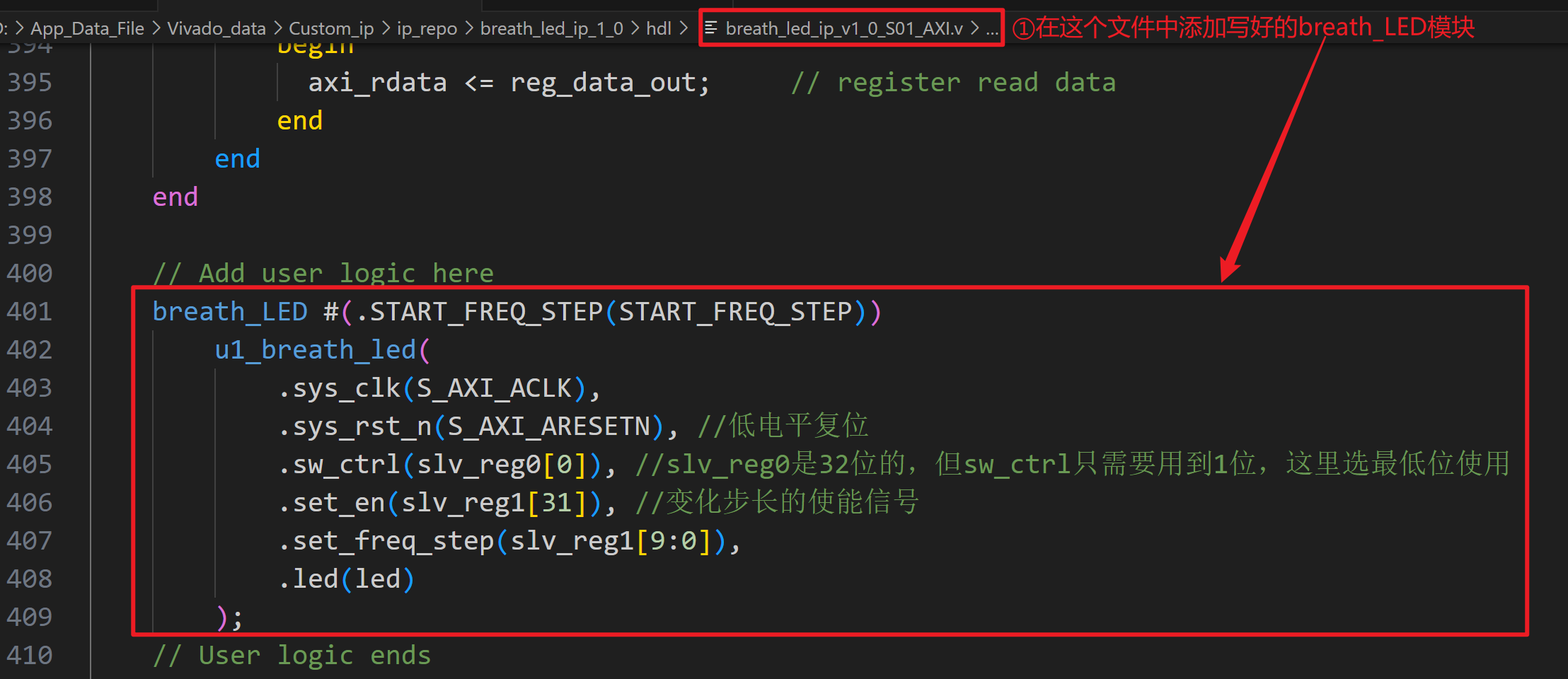

编写呼吸灯模块代码并在ip核中例化

模块添加:

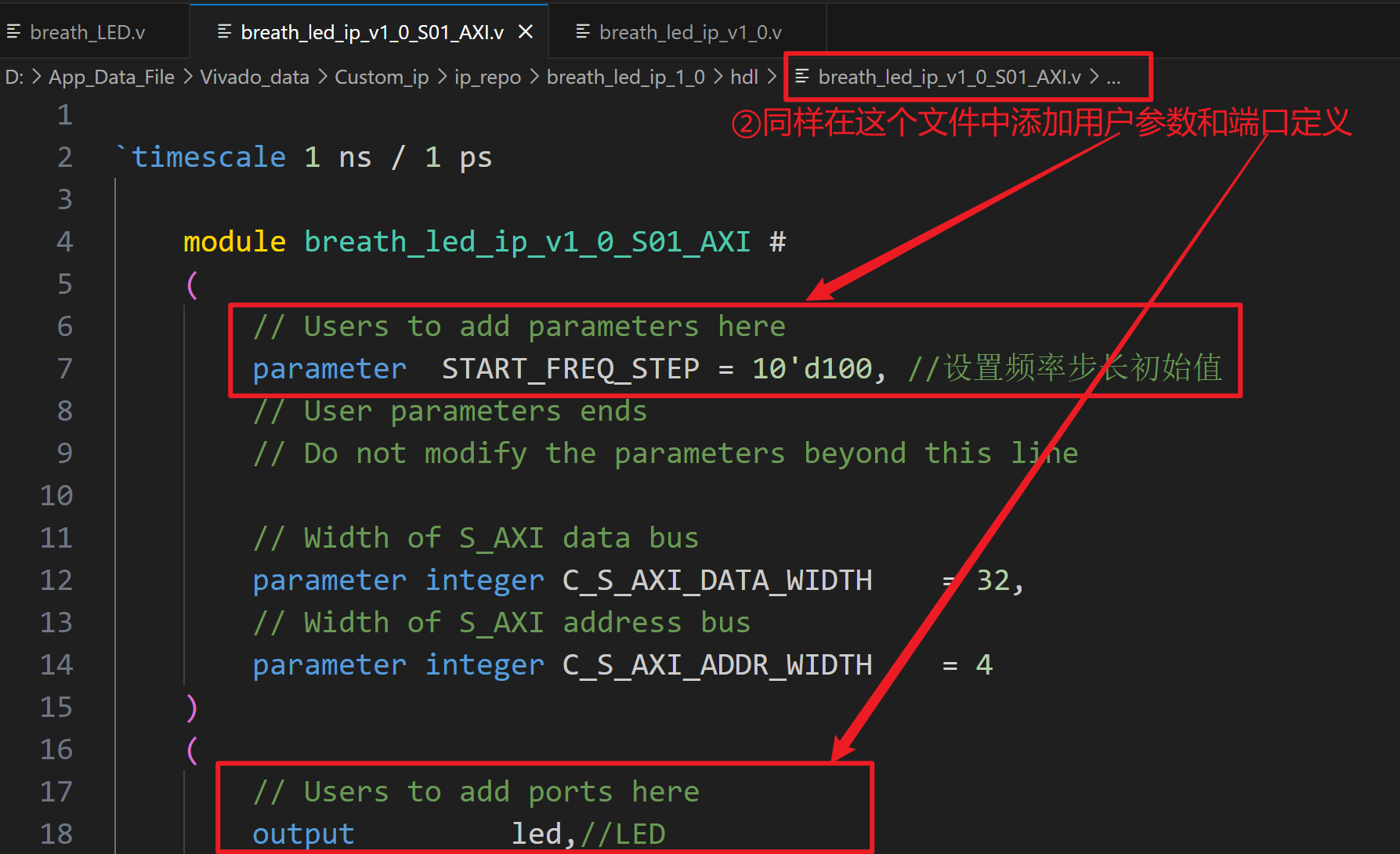

添加参数和自定义的输入或输出端口

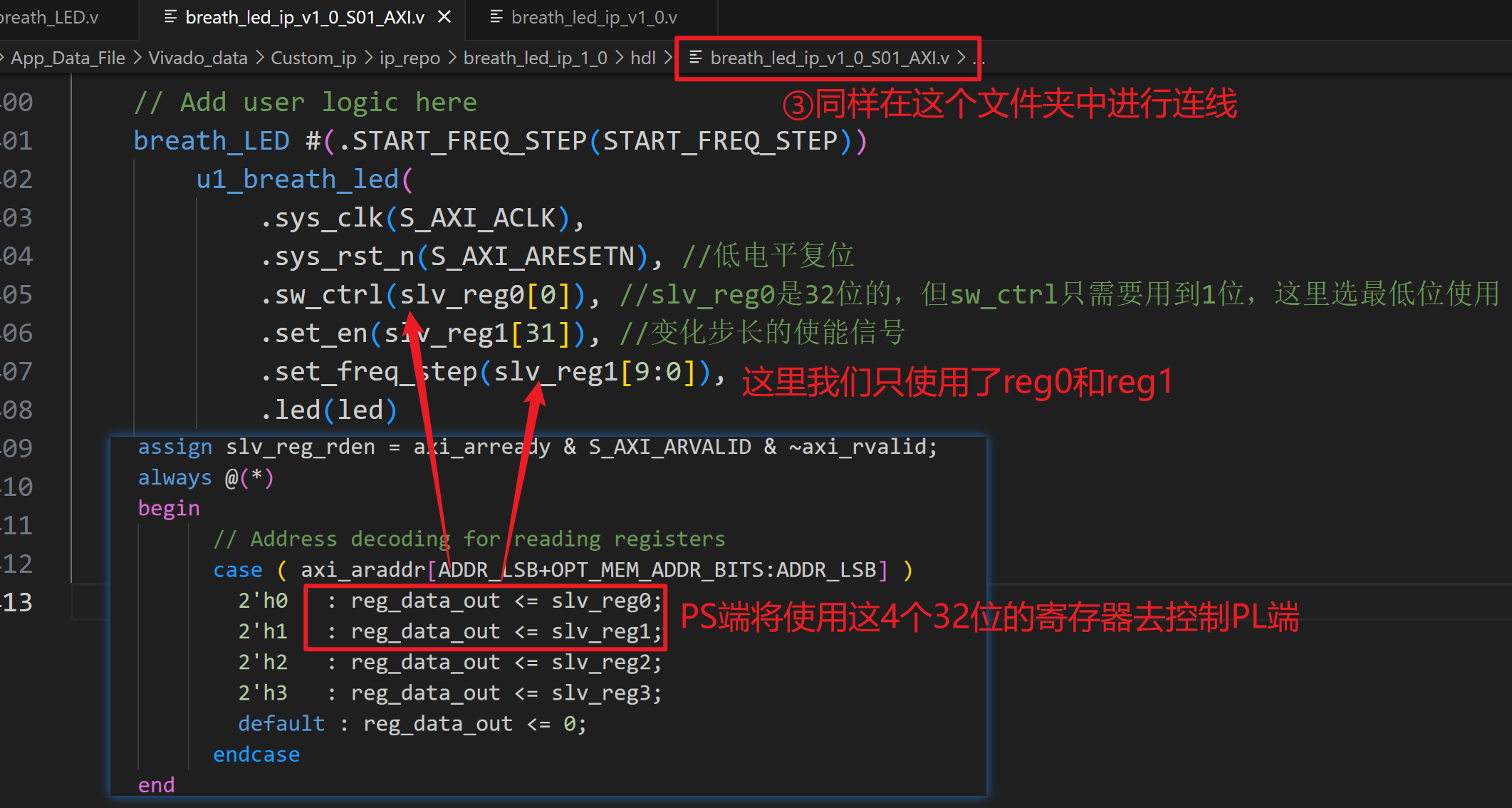

端口连线

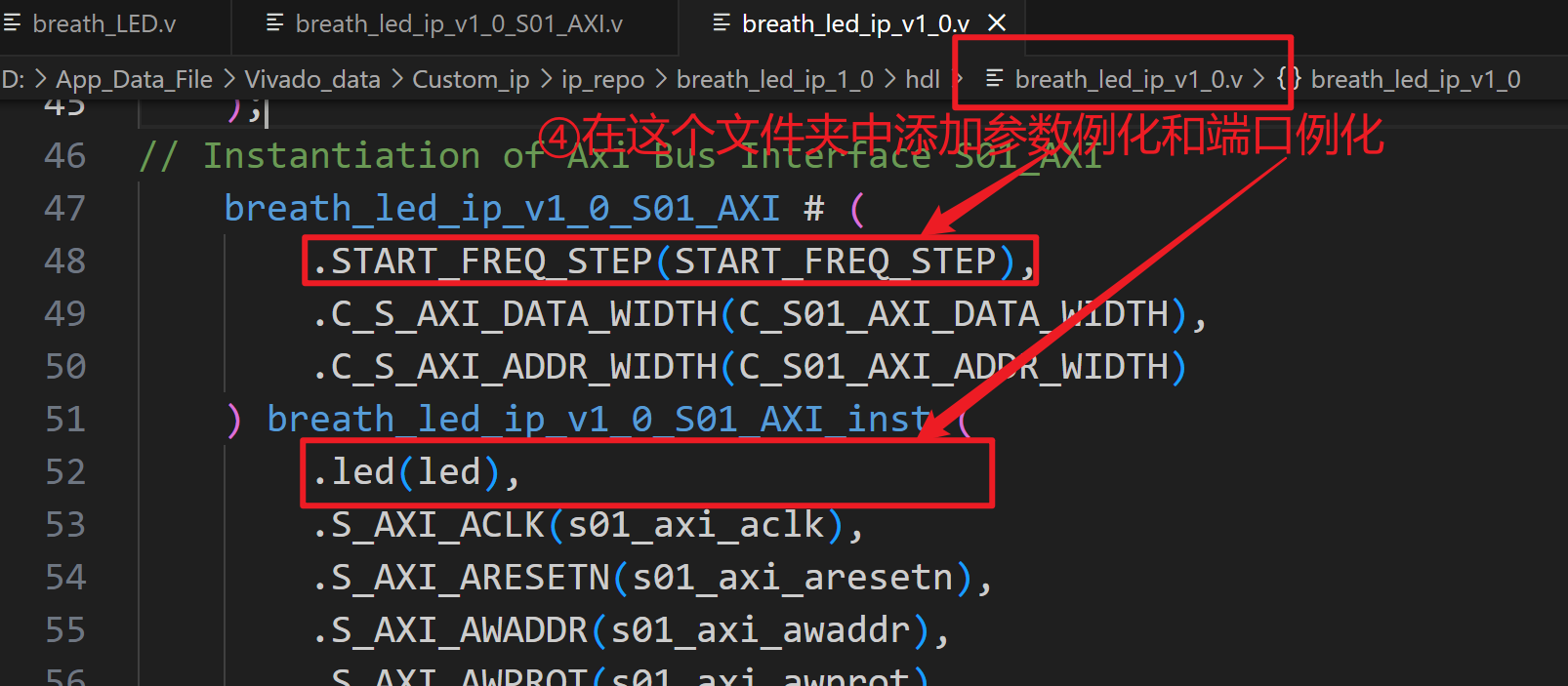

在IP的顶层文件中添加参数和端口的例化

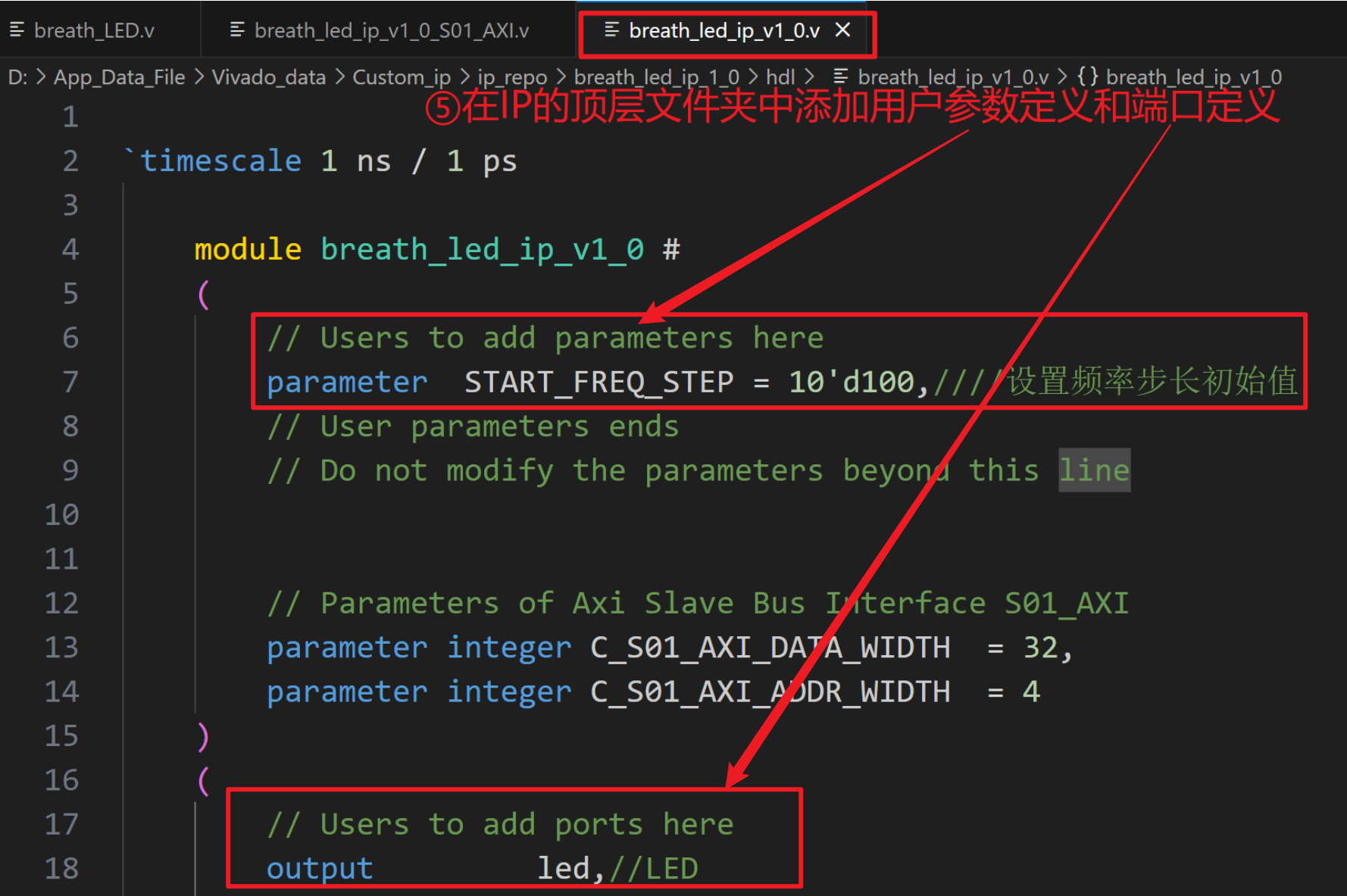

同样也需要在顶层文件中添加自定义的输入或输出端口和相关参数

3.IP核的封装

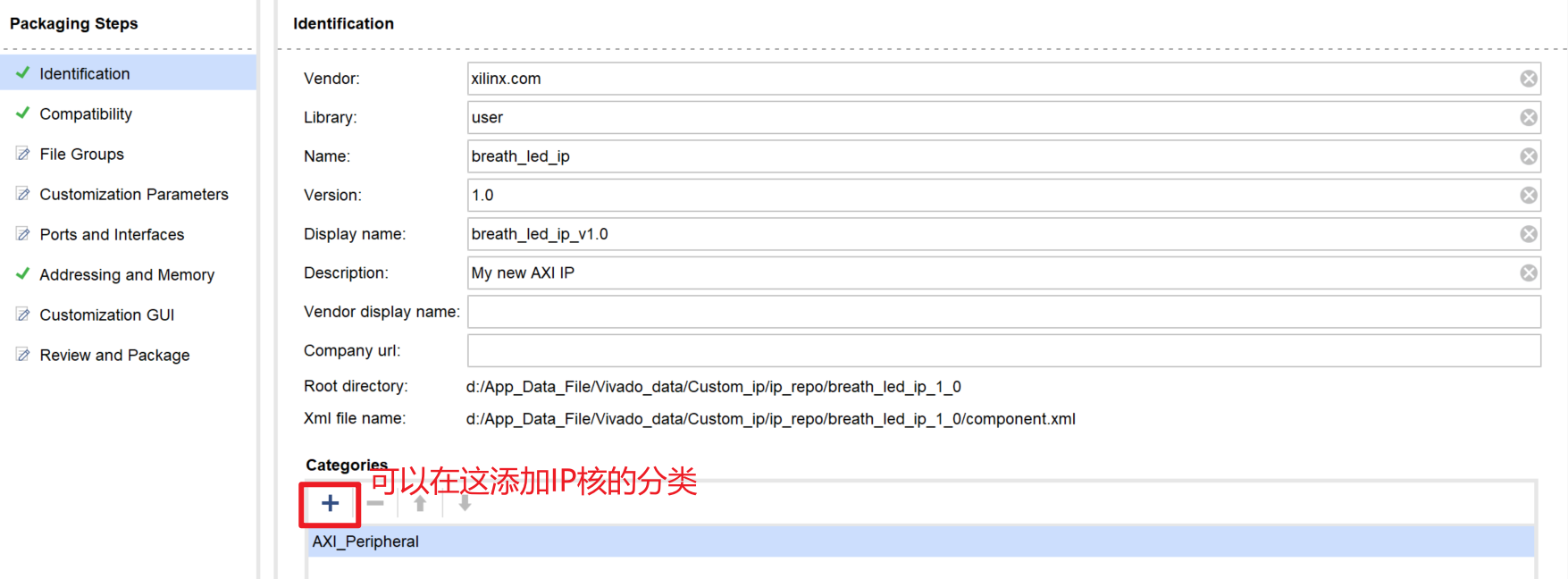

Identification:

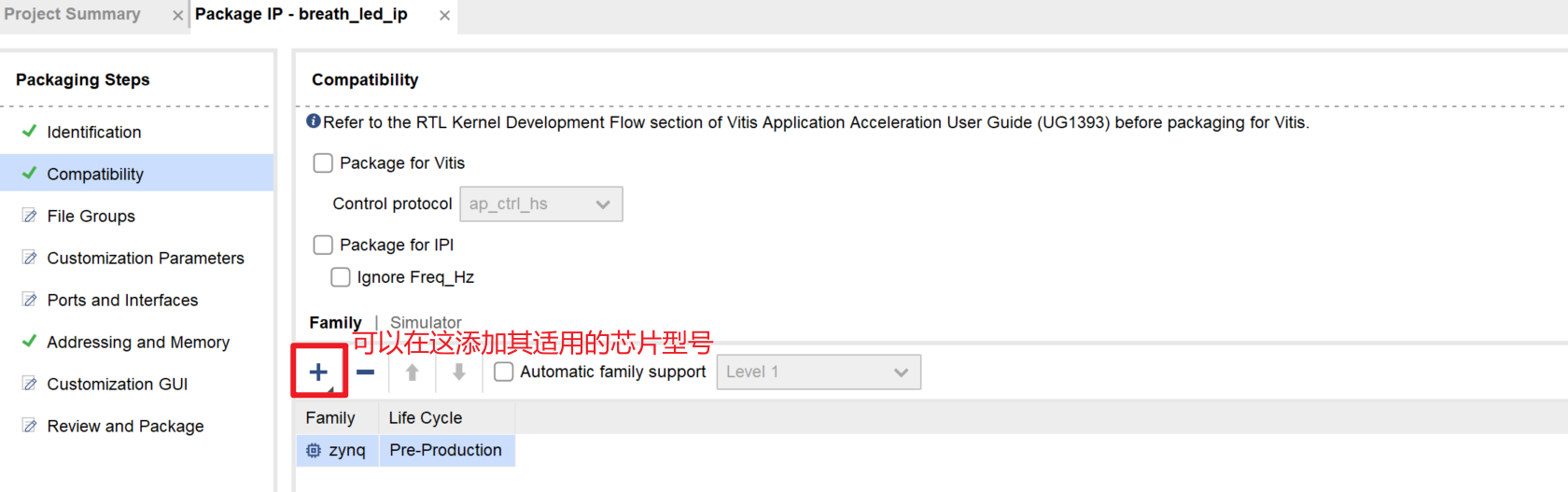

Compatibility:

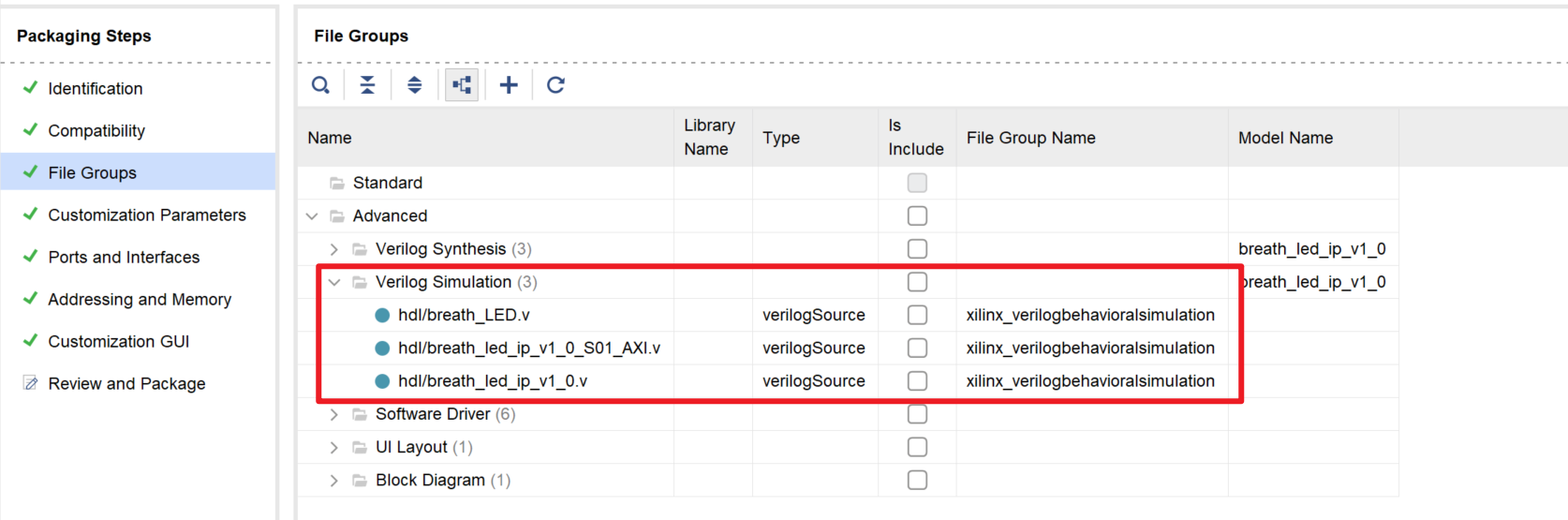

File Groups:可以预览 IP 核包含的相关源码文件,在源码工程中包含的所有Verilog源码或者仿真测试脚本,也都会出现在这里,被集成到IP核中

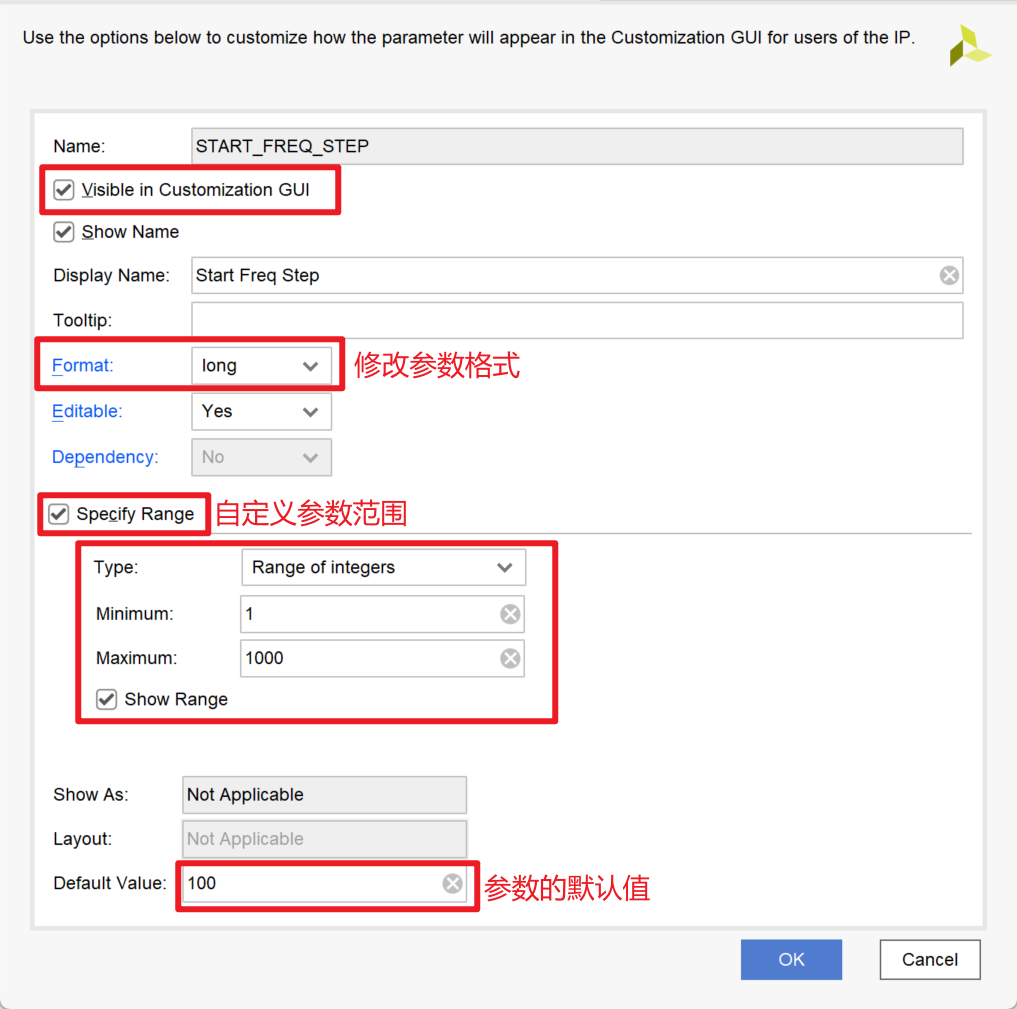

Customization Parameters:配置相关参数

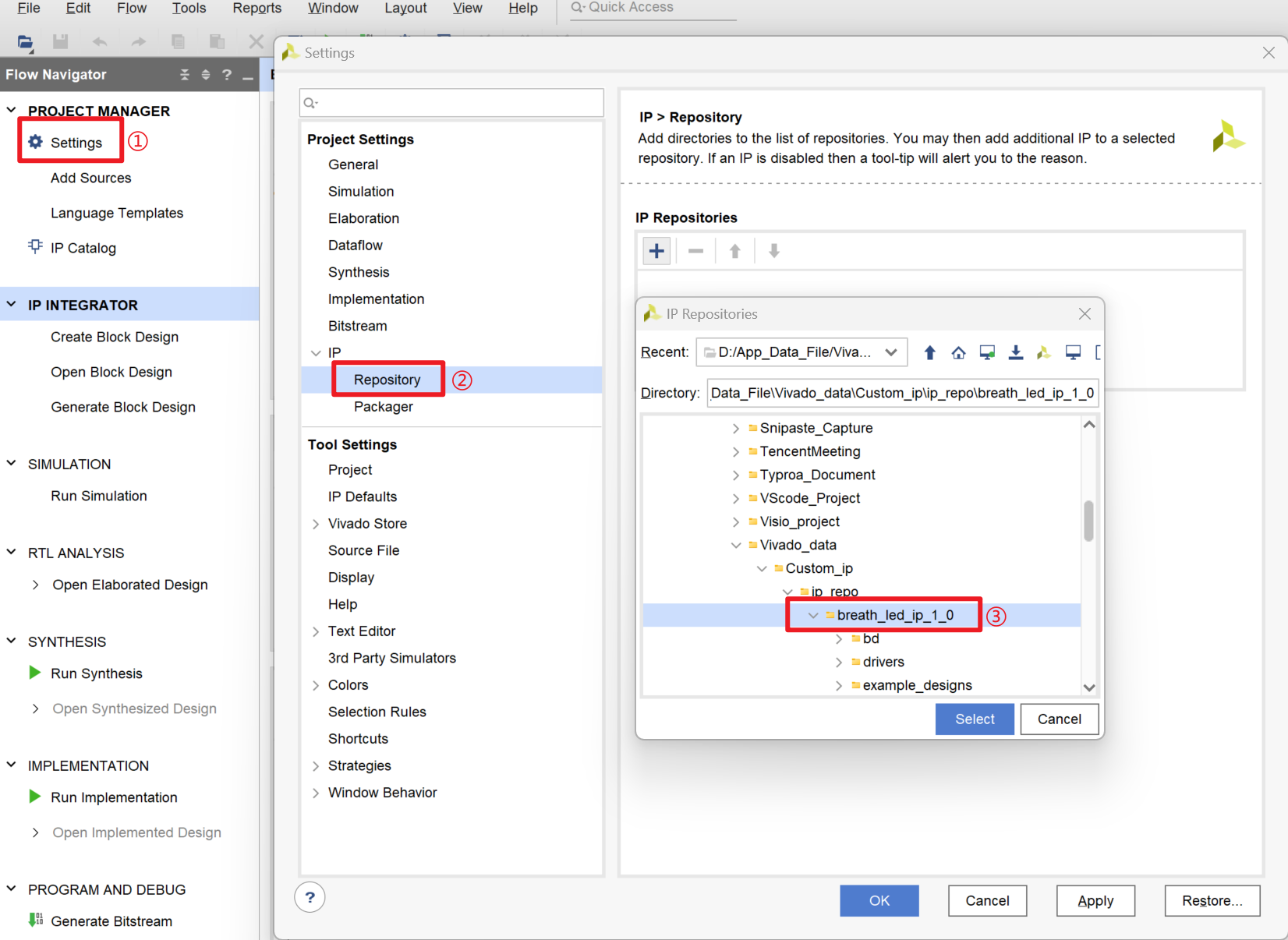

4.IP核的添加

自定义IP核的应用-呼吸灯

实验任务:通过自定义一个LED ip核,来控制PL LED呈呼吸灯效果,并且PS可以通过AXI接口来控制呼吸灯的开关和呼吸的频率

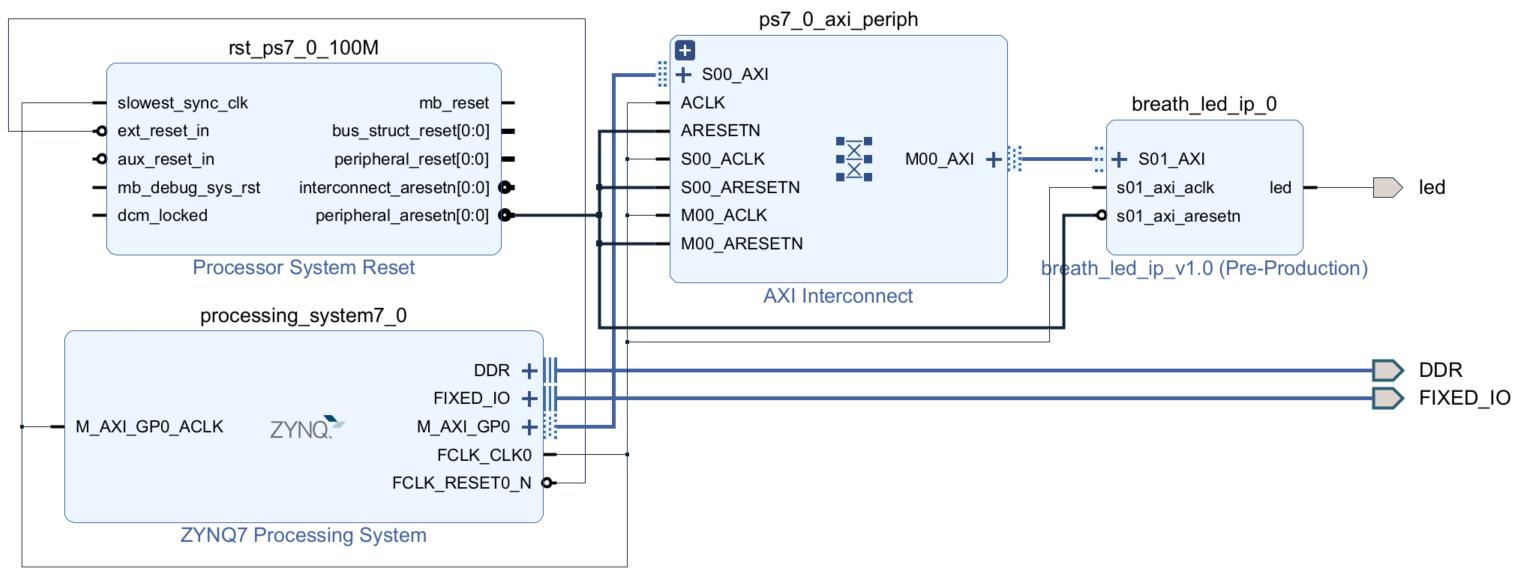

1.Vivado中的block design

直接加载zynq芯片与breath_led的IP核,点击自动配置与自动连线,最终block design的设计图如下:

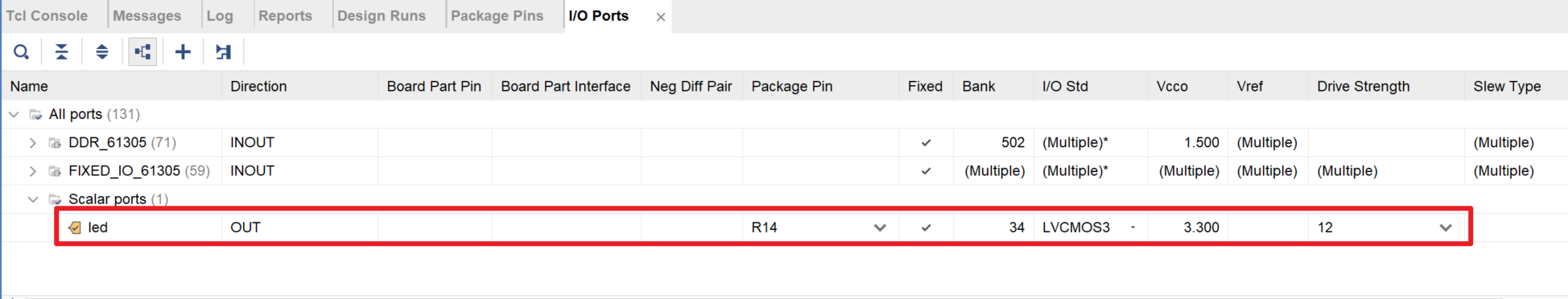

led的管脚分配

2.Vitis中代码编写

- LED灯先快闪5s之后,休息1s,开始慢闪

1 |

|

由于自定义IP导入Vitis,会出现一个bug

解决办法参考:

我的makefile文件如下:

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29COMPILER=

ARCHIVER=

CP=cp

COMPILER_FLAGS=

EXTRA_COMPILER_FLAGS=

LIB=libxil.a

RELEASEDIR=../../../lib

INCLUDEDIR=../../../include

INCLUDES=-I./. -I${INCLUDEDIR}

INCLUDEFILES=$(wildcard *.h)

LIBSOURCES=$(wildcard *.c *.cpp)

OUTS = $(addsuffix .o, $(basename $(wildcard *.c)))

OBJECTS = $(addsuffix .o, $(basename $(wildcard *.c *.cpp)))

ASSEMBLY_OBJECTS = $(addsuffix .o, $(basename $(wildcard *.S)))

libs:

echo "Compiling breath_led_ip..."

$(COMPILER) $(COMPILER_FLAGS) $(EXTRA_COMPILER_FLAGS) $(INCLUDES) $(LIBSOURCES)

$(ARCHIVER) -r ${RELEASEDIR}/${LIB} ${OUTS}

make clean

include:

${CP} $(INCLUDEFILES) $(INCLUDEDIR)

clean:

rm -rf ${OUTS}