本节主要介绍了SystemVerilog中比verilog更好用的相关特性以及在基础语言上扩展的接口。

过程语句块新特性

- always语句块被细分为了:

- 组合逻辑语句块:

always_comb - 锁存逻辑语句块:

always_latch - 时序逻辑语句块:

always_ff

- 组合逻辑语句块:

1.过程语句块always_comb

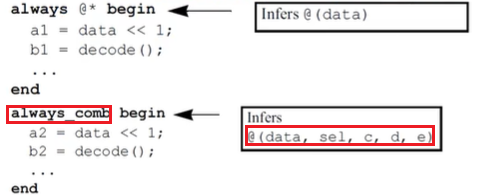

always_comb用来表示组合逻辑

always_comb可以自动嵌入敏感列表

always_comb可以禁止共享变量,即赋值左侧的变量无法被另一个过程块所赋值

always_comb在仿真0时刻会自动触发一次,无论在0时刻是否有敏感信号列表中的信号发生变化

软件工具会检查该过程快,如果其所表示的不是组合逻辑,那么会发生警告

1

always_comb if (en) y=a; //此时软件工具会报警告

Verilog @*的敏感列表声明方式不同于always_comb:

always_comb会限制其他过程块对同一变量进行赋值

always_comb会将被调用函数中可能参与运算的其他信号也声明到敏感列表中

2.过程语句块always_latch

always_latch表示锁存逻辑,且自动插入敏感列表

EDA工具会检查always_latch过程块是否真正实现了锁存逻辑

1

2always_latch

if (enable) q <= d;

3.过程语句块always_ff

always_ff用来表示时序逻辑

敏感列表必须指令posedge或者negedge

EDA工具也会检明always_ff过程块语句是否实现了时序逻辑

1

2

3always_ff @(posedge clock, negedge resetN)

if (!resetN) q <= 0;

else q <= d;

赋值操作符

SV可以通过

'0,'1,'z和'x来分别填充0、1、z、和x,通过这种方法,代码会根据向量的宽度自动填充SV添加了

inside操作符,用来检查数值是否在一系列值的集合当中1

2logic [2: 0] a;

if (a inside {3'b001, 3'b010, 3'b100})

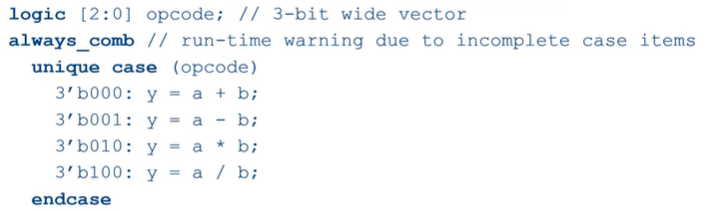

增强的case语句

unique case要求每次case选择必须只能满足一条case选项

priority case则表示必须至少有一个case选项满足要求,如果有多个case选项满足要求时,第一个满足的分支将会被执行

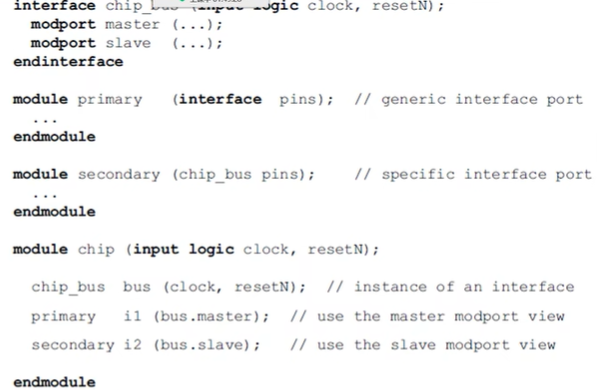

接口

接口不单单可以包含变量或者线网,它还可以封装模块之间通信的协议

接口无法例化module,但是接口可以例化接口

接口中可以进一步声明

modport来约束不同模块连接时的信号方向接口信号必须采用非阻塞赋值来驱动

组合逻辑、锁存器、时序逻辑相关

- 为什么if不加else会生成锁存器?6.5 Verilog 避免 Latch | 菜鸟教程 (runoob.com)